# **NanoElectronics Roadmap for Europe**

From Nanodevices and Innovative Materials to System Integration

https://www.nereid-h2020.eu/roadmap

III. Conclusion &

Equipment & Manufacturing

Energy Harvesting/Storage & Het. Integration

Smart Sensors

11.1 Advanced Logic/Memories

#### Abstract

The NEREID project ("NanoElectronics Roadmap for Europe: Identification and Dissemination") is dedicated to mapping the future of European Nanoelectronics. NEREID's objective is to develop a medium and long term roadmap for the European nanoelectronics industry, starting from the needs of applications to address societal challenges and leveraging the strengths of the European eco-system. The roadmap will also identify promising novel nanoelectronic technologies, based on the advanced concepts developed by Research Centres and Universities, and potential bottlenecks along the innovation (value) chain. Industry applications include Energy, Automotive, Medical/Life Science, Security, IoT, Mobile Convergence and Digital Manufacturing. The NE-REID roadmap covers Advanced Logic and Connectivity, Functional Diversification (Smart Sensors, Smart Energy and Energy for Autonomous Systems), Beyond-CMOS, Heterogeneous Integration and System Design as well as Equipment, Materials and Manufacturing Science.

The project solicits application and technology experts from leading industrial and academic research organizations to participate to General and Domain Workshops, which allow the consortium to better define the technology roadmap according to application requirements and technology evolution. Structured discussion and debate provide the convergence between applications and technologies.

This common work between technology and application experts leads to the early identification of the most promising technologies needing additional R&D actions, which could be very useful for the future electronic products of European companies leading to a strong impact on the European economy and society. The NEREID Nanoelectronic Roadmap takes into account the specificity of the European industrial and academic landscape, and is very important to better coordinate academic and industrial research for equipment, semiconductors and application developments. It will be used as input for future research programmes at European and National levels in order to join efforts to overcome the main nanoelectronic challenges and put the EU at the forefront of future technological developments.

## **Table of Contents**

| I.    | General Introduction                             | 3   |

|-------|--------------------------------------------------|-----|

| 1.1   | Roadmapping Process                              | 3   |

| I.2   | Application domains                              | 3   |

| 1.3   | Interactions with other international activities | 4   |

|       | Nanoelectronic Technology Sectors                |     |

| .1    | Advanced Logic and Memories                      | 6   |

| 11.2  | Connectivity                                     | 23  |

| 11.3  | Smart Sensors                                    | 40  |

| 11.4  | Smart Energy                                     | 58  |

|       | Energy for autonomous systems                    |     |

| 11.6  | System Design and Heterogeneous Integration      | 81  |

|       | Equipment and Manufacturing Science              |     |

| 11.8  | Beyond CMOS                                      | 104 |

| III.  | General                                          |     |

|       | General recommendations                          |     |

| 111.2 | General Conclusion                               | 117 |

#### Acknowledgement

The H2020 NEREID Coordination and Support Action (n° 685559) entitled "NanoElectronics Roadmap for Europe: Identification and Dissemination" has been funded by the European Commission following the Nanoelectronics call "H2020-ICT-2015 Generic micro- and nanoelectronic technologies" and has been launched at the European Nanoelectronics Forum in Berlin in December 2015 for a duration of 3 years.

#### I. General Introduction

3

Roadmaps are highly beneficial for all high tech sectors, like Nanoelectronics, to improve links between academic and industrial research, to drive investments, to provide inputs for future research programmes and to coordinate efforts to overcome the main technology challenges.

For more than 20 years, the International Technology Roadmap for Semiconductors (ITRS) has guided the industry to follow Moore's Law, with a constant reduction in device costs and an exponential growth of the semiconductor market. The main role of ITRS has been in providing re-search guidance for the many actors of the semiconductor ecosystem, in synchronizing the technology development and the timely availability of manufacturing equipment and methods and in providing focus on critical bottlenecks.

However, the "technology push" that has been at the base of ITRS has shown in recent years its limits: device size and speed are no longer the only parameters of importance, and system-driven technologies have been considered by the new IRDS Roadmap (International Roadmap for Devices and Systems), focusing on computing systems.

On the other hand, the integration of new functionalities, required by new applications, needs the incorporation of special metrics for technologies that do not necessarily scale according to "Moore's Law", expanding the focus from chips to different kinds of systems. This trend is especially relevant for the European semiconductor industry that has focused on segments of greater relevance for the European industry applications, like Automotive, Industrial and Medical. Therefore, an appropriate kind of roadmap is needed for Europe which focuses on Nanoelectronics with respect to the European abilities and strengths. The objective of the NEREID project is to elaborate a new roadmap for Nanoelectronics, focused on the requirements of European semiconductor and applications industry to address societal challenges, and the advanced concepts developed by Research Centres and Universities in order to achieve an early identification of promising novel technologies covering the R&D needs all along the innovation chain. The final result is a roadmap for European micro- and nanoelectronics, with a clear identification of medium and long term objectives. The roadmap is divided into main technology sectors: Advanced Logic (including Nanoscale FETs and Memories) and Connectivity, Functional diversification (Smart Sensors. Smart Energy, Energy for Autonomous Systems). Beyond CMOS (Emerging devices and Computing Paradigms), Heterogeneous Integration and System Design, Equipment, Materials and Manufacturing Science, and also includes cross-functional enabling domains.

Understanding the dependencies between short/medium term (e.g. More Moore and More than Moore) and long/ very long term (e.g. Beyond CMOS) activities is also very important to speed-up technology transfer between academia and industry using disruptive technologies leading to possible new large future markets.

The NEREID Roadmap, focused on medium and long term time horizons, is complementary to the AENEAS/ ECS Strategic Research Agenda and the ECSEL MASRIA, which are focusing on shorter terms. NEREID is also planning the evolution of the main Figures of Merit (FoM) vs time horizon for the most promising technologies, which are not included in the ECS SRA. NEREID has some commonalities and is developing joint collaboration with the new International IRDS Roadmap especially in the fields of More Moore, Beyond CMOS and computing systems, but is also complementary to IRDS with very important NEREID activities in the More than Moore domain (e.g. Smart Sensors, Smart Energy, Energy Harvesting), which is a sound European competence, leading to a large diversity of electronic systems useful for many applications. In

the More Moore field, there are also strong interests in Europe for specific activities dealing with very low power systems, leading to possible disruptive applications for instance for future internet of things (IoT) systems, or for application driven performance, e.g. high temperature operation for the automotive industry.

Therefore, the NEREID Roadmap takes into account the specificity of the European industrial and academic landscape, and will be very important to better coordinate academic and industrial research for equipment, semiconductors and application developments, as well as serving as the input for future research programmes at European and National levels in order to coordinate efforts to overcome the main nanoelectronic challenges and put the EU at the forefront of future technological developments.

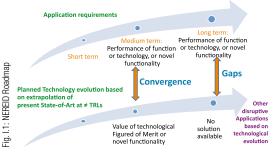

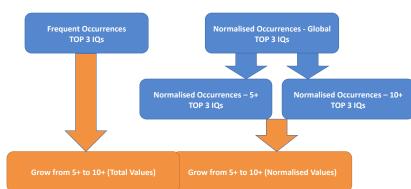

#### I.1 Roadmapping Process

The project supported the participation of many application and technology experts, coming from leading research actors in industry and academia, to workshops during which they presented the state-of-the-art. Three major general Workshops and many Domain Workshops (for WPs and Tasks) have been organized with a large participation by European application experts/technology users and technological experts (more than 100 experts) in order to better define the technology roadmap in terms of applications requirements and technology evolution, and discuss the convergence between applications and technologies (s. figure I.1 on next page). The proposed idea is that the scenarios of evolution of the products/applications will result in performance evolution scenarios for the functions, which could be generic enough to apply to many products. The next step is then to derive, from the evolution of functions, the evolution of the underlying technologies and devices using the expertise of technology experts. Insights on future technology evolution and availability can also prompt new ideas for disruptive products and applications, which are discussed in Domain Workshops and also presented by technology experts during the General Workshops.

This common work between technology and application experts is leading to the early identification of the most promising technologies needing additional R&D activities in order to become useful for the future electronic products of European companies, thus leading to a strong impact on the European economy and society.

The important assets of NEREID are the following:

- the projection of the evolution of many Figures of Merit (FoM) vs time for covering the most promising technologies including novel functionalities

- the understanding of the dependencies between short/ medium term (e.g. More Moore and More than Moore) and long/very long term (e.g. Beyond CMOS) activities

- the strong interaction between application and technology experts, coming from leading research players in industry and academia, especially with the organization of many Workshops.

- the combination of a top-down approach, which is application driven, and a bottom-up one, based on planned technology evolution to prompt new ideas for disruptive products and applications (s. figure I.1 on next page).

#### I.2 Application domains and Societal benefits of a new European Roadmap

We have proposed to start from the different very important European application areas (Energy, Automotive, Medical/Life science, Security, IoT/Smart connected objects, Mobile convergence, Digital Manufacturing) in order to define the roadmap.

We have therefore invited potential users of the nanoelectronic technologies in the NEREID General Workshops to provide insight on the technology requirements in terms of both performance and timescale for the future applications and/or (generic) functions envisioned by their Companies.

These requests are then used by technology experts for the identification of the most promising technologies and functions that can satisfy the functionalities and performances needed for these different applications.

#### Societal benefits

Future electronic systems will play a vital role in all of the very important European application areas mentioned above. The world of connected objects and the development of "Smart Everything Everywhere", with huge future markets, imply the development of dedicated technologies like low power devices and the

development of many new functionalities for sensing, computing, communicating, energy harvesting, etc.

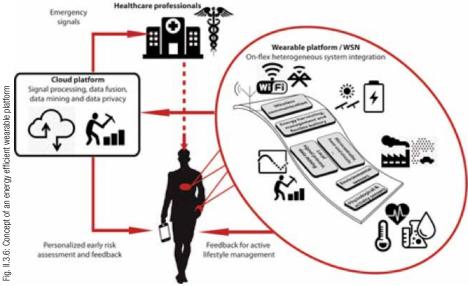

The use of renewable energy sources is becoming one of the most important topics in our society. Among the benefits, it is possible to envisage the development of autonomous, wearable, or even implantable sensor nodes for health applications or environmental monitoring for instance. The development of "green" materials, replacing toxic/rare materials used nowadays, is also of paramount importance for future sustainable systems and society.

On the other hand, the estimated energy saving potential that can be achieved by introducing power electronics into systems is enormous, estimated at more than 25% of the current electricity consumption in the EU countries1. Since power electronics is a key technology in achieving a sustainable energy society, the demand for power electronics solutions will show significant growth in the coming decades.

In the health sector, the strong incidence of chronic diseases, such as cancer, cardiovascular diseases, obesity, diabetes, autoimmune and psychiatric diseases will increase the demand for diagnostic devices (activity trackers, body monitors and multi-parameter real-time sensing) and for most devices a low-cost, portable and fast diagnostic solution does not exist in the market yet. Moreover, similar devices could also serve to detect the incidence of health hazards caused by pollution (air quality, water and food monitoring, ...) and address rising concerns about health and well-being. These emerging medical devices (wearable sensors, implantable sensors and others) would

1 Quotations from the CATRENE White Book: Public Final Report of the E4U Project Electronics enabling effi energy usage, funded by the European Commission's ICT programme in FP7 (project no. 224161), 2009 (2) J. Popovic, Gerber et al, "Power electronics enabling efficient energy usage: energy savings potential and technological challenges ", IEEE Transactions on Power Electronics, vol. 27, no. 5, pp. 2338 -2353, May 2012

benefit healthcare facilities and simplify the acceptance of personalized, more-efficient medicines.

The connectivity functions will be everywhere in the future connected world, starting from the physical world, e.g. the things and the persons, the autonomous objects, factory 4.0, to the cloud.

An early consideration of all these trends, which have been taken into account in the NEREID Roadmap, will be beneficial to the EU. NEREID will lead to disruptive technologies and applications and many new markets, strengthening the international position of the European economy and having a great potential impact on the European society.

# I.3 Interactions with other international activities

The activities of NEREID account for the international context of roadmapping through the Advisory Board that include personalities involved in USA and Asia in similar activities. They are proving systematic feedback about the coherence and complementarity of NEREID with the global context, while constructively recognizing the European focus on priorities, specific to NEREID.

On the other hand, NEREID has concretely started and implemented a series of actions of reciprocal benefits with the International Roadmap of Devices and Systems (IRDS) supported by IEEE organization. In fact, almost simultaneously with the launch of NEREID, in May 2016, IEEE announced the formation of the IRDS under their sponsorship to address the mapping of the ecosystem of newly reborn electronics industry. The migration from ITRS to IRDS is proceeding seamlessly, with all reports produced in the past by the ITRS 2.0 representing the starting point, and including contributions and groups from USA, Asia and Europe (i.e. an international dimension). The first IRDS Roadmap (2017) has been published in June 2018. This was a unique opportunity for NEREID to forge a partnership with IRDS and have reciprocal participation in meetings, and building a vision about the future of Nanoelectronics, to which each initiative contributes with its specific strong points. Of particular importance is the concrete actions taken to compare roadmaps between NEREID and IRDS in the following fields, in which the interests of the two initiatives overlap:

- Systems and Architectures: Cloud computing, IoT, Smartphone, Cyber Physical systems,

- Outside System Connectivity: RF & Analog & Mixed Signal, Photonic Interconnects,

- Beyond CMOS: Emerging memory and storage devices, Emerging information processing and logic devices, Emerging devices for functional diversification, Interface between emerging devices and novel computing architectures/paradigms,

- Metrology,

- Yield

- More Moore: Logic technology

NEREID was also in charge of the "long term Grand Challenges" of the IRDS Roadmap, which has been published in the Executive Summary of IRDS.

Therefore, NEREID has also developed collaboration with, and is in part complementary to, the IRDS in the Europe-led More than Moore domain (e.g. Smart Sensors, Energy, Energy Harvesting) leading to beyondcomputing systems.

With its mid/long term focus, the NEREID Roadmap is also complementary to the European ECSEL ECS Strategic Research Agenda, which is focusing on shorter term horizons.

#### II. Nanoelectronic Technology Sectors

#### **Overview on Technology Sectors and their Main Concepts**

The NEREID roadmap is structured by the following nanoelectronic technology sectors, which are covered in the following Chapters (II.1 to II.8). Within all these technology sectors the roadmap follows a fixed structure which addresses the technologies' relevance, its competitive value, its vision, its scope and ambition, its synergies with other topics and its main concepts. Finally, each chapter ends with some recommendations for the technology sector.

On this page, all technology sectors are listed with all the main concepts that have been considered in the NEREID roadmap.

#### II.1 Advanced Logic and Memories (NEREID TASK 3.1)

- Nanowires

- FinFET

- FD-SOI

- Negative Capacitance FET (NCFET)

- Carbon Nanotubes (CNTFET)

- Memories, Concept 1 OxRAM:

- Memories, Concept 2 CBRAM

- Memories, Concept 3 PCM

- Memories, Concept 4 MRAM

- 3D sequential integration

- Reliability

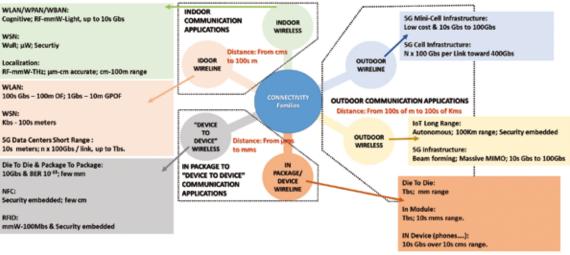

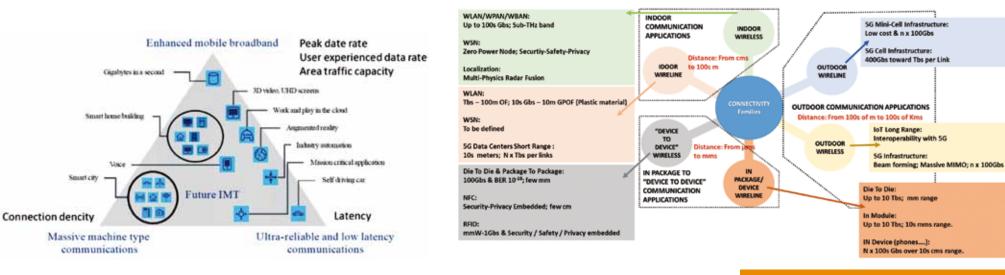

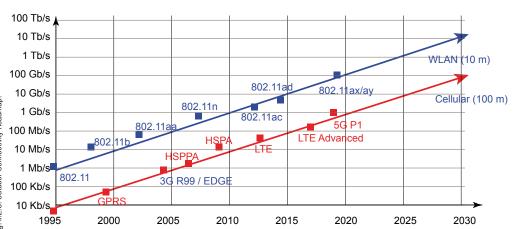

#### II.2 Connectivity (Wireline and Wireless) (NEREID TASK 3.2)

- The Outdoor Wireless Applications

- The Outdoor Wireline Applications

- The Indoor Wireless Applications

- The Indoor Wireline Applications

- The Device to Device Wireless Applications

- The In Package/Device Photonics Wireline Applications

#### II.3 Smart Sensors (NEREID TASK 4.1)

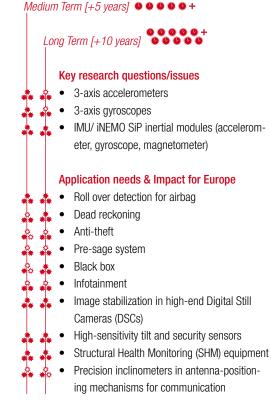

- Sensor's for car internal system performance

- Motion and Pressure sensors

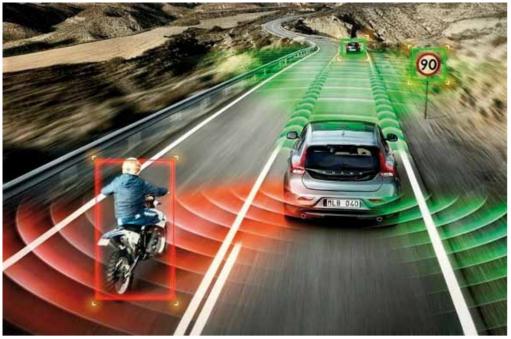

- Advance Driver Assistance System (ADAS)

- Image Sensors-, Radar LiDAR- and Infrared sensors

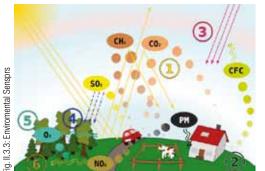

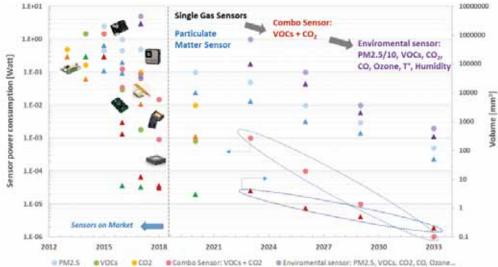

- Environmental monitoring:

- Gas and Particulate Matter sensors

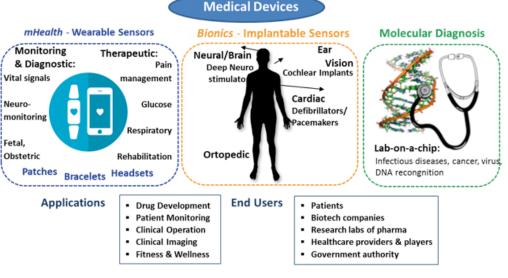

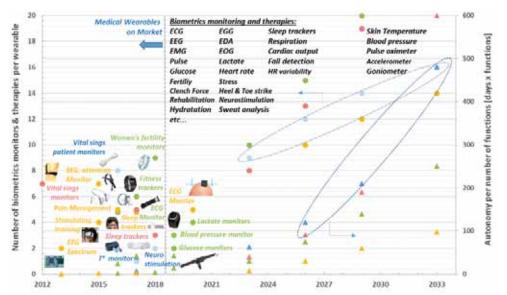

- Sensors for medical and healthcare

- Physiological signal monitoring

- Implantable sensors

- Molecular diagnostics

#### II.4 Smart Energy (NEREID TASK 4.2)

- Si based power devices

- GaN-devices and substrates

- SiC-based substrates

- Alternative Wide Bandgap Semiconductors

#### II.5 Energy for Autonomous Systems (NEREID SubTASK 4.2.11)

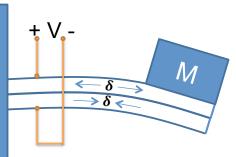

- Mechanical EH: Electrostatic transduction

- Mechanical EH: Piezoelectric transduction

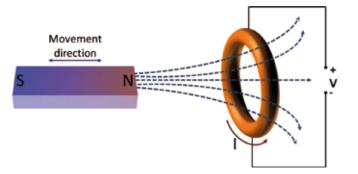

- Mechanical EH: Electromagnetic transduction

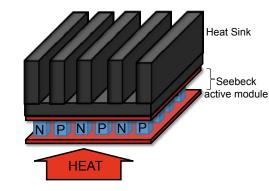

- Thermal energy harvesting

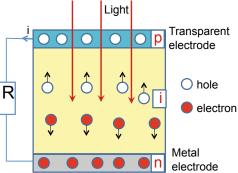

- Photovoltaic Energy Harvesting

- RF energy harvesting/wireless power transfer

- Energy storage Microbatteries

- Energy storage Microcapacitors

- Micro-Power Management

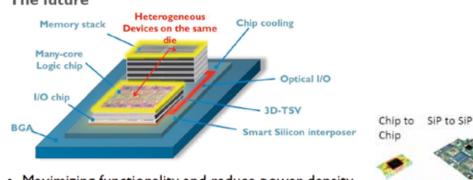

#### II.6 System Design and Heterogeneous Integration (NEREID Workpackage 5, WP5)

In this chapter, the main concepts are classified by connecting the three applications

- Automated Driving;

- Implantable Devices;

- Environmental Monitoring and Wearable Systems,

- with different elements of Application-Aware Hardware-Software-Co-Design. These Elements comprise Functionalities, Implementation Qualities and Criticalities and Needs.

#### II.7 Equipment and Manufacturing Science (NEREID Workpackage 6, WP6)

- More Moore

- More-than-Moore

- Manufacturing Science

#### II.8 Beyond-CMOS – Emerging devices and Computing Paradigms (NEREID Workpackage 2, WP2)

- Steep slope switches: Tunnel FETs

- Neuromorphic circuits and computing

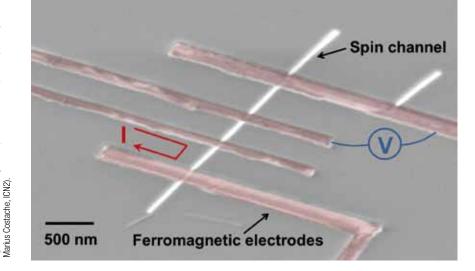

- Spintronics

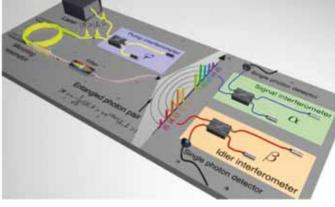

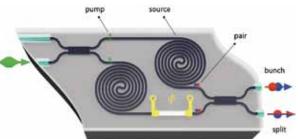

- Quantum Photonics

- Phonon, Brownian and nano-opto-mechanical computing

#### **II.1 Advanced Logic and Memories**

#### **Executive summary**

The historical trend in micro/nano-electronics over the last 40 years has been to increase both speed and density by scaling down the size of electronic devices, together with reduced energy dissipation per binary transition, and to develop many novel functionalities for future electronic systems. We are facing today dramatic challenges for More Moore and More than Moore applications: substantial increase of energy consumption and heating which can jeopardize future IC integration and performance, reduced performance due to limitation in traditional high conductivity metal/low k dielectric interconnects, limit of optical lithography, heterogeneous integration of new functionalities for future nanosystems, etc.

Therefore many breakthroughs, disruptive technologies, novel materials, and innovative devices are needed in the next two decades.

With respect to the substantial reduction of the static and dynamic power of future high performance/ultra low power terascale integration and autonomous nanosystems, new materials, ultimate processing technologies and novel device architectures (FD-SOI, FiNFET, Nanowire FET, Carbon Nanotube FET, Ferroelectric Gate FET with Negative Capacitance, Non-charge-based Memories, 3D integration) are mandatory for different applications using ultimate CMOS, as well as new circuit design techniques, architectures and embedded software.

This section will focus on the main trends, challenges, limits and possible solutions for future high performance and ultralow power nanoscale devices in the CMOS arena.

#### **Relevance and competitive value**

What are the advantages of the chosen technologies (concepts) compared to others?

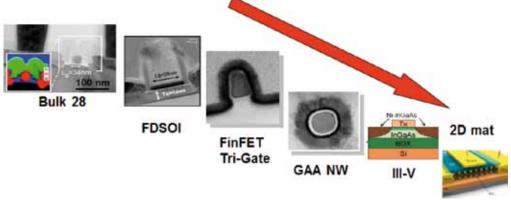

During decades, Moore's law was the main driver of the CMOS world, and most of the electronic industries were scaling the CMOS area by a factor 2 every 2 years. At the 32/28 nm node, the industry introduced the first CMOS revolution by leaving the classical bulk CMOS integration to shift to thin-film devices for improved electrostatic control.

In this way, STMicroelectronics introduced the 28FD-SOI, and companies like INTEL, Samsung and TSMC have shifted to FinFET technologies and are continuing down to the 10 and 7 nm node. In this context, the CMOS world is facing a second revolution, as the famous Moore's law slows downs because cost and complexity of scaling are increasing faster than economic advantages. The technology-push approach that has driven semiconductor evolution is slowing down, while the market is shifting to a more application-driven approach. This implies that technology differentiation is becoming again a critical issue for semiconductor actors.

#### Vision

For future, reliable, high performance and/or low power ICs and systems, new materials (strained semiconductors, SiGe, Ge, III-V, 2D, 1D, Ferroelectric, Carbon), ultimate processing technologies and novel device architectures (FD-SOI, FinFET, Nanowire FET, CNTFET, NCFET, Non-charge-based Memories, 3D integration) are required. In the field of alternative memories, PCRAM, RRAM, MRAM, or Ferrolectric RAM will be useful for pushing the limit of integration and performance beyond those afforded by present Non-Volatile, DRAM and SRAM memories.

3D sequential processes could also be used for the integration of these future high performance sustainable, secure, ubiquitous and pervasive systems, which will be of high added value for many applications in the field of detection and communication of health problems, environmental quality and security, secure transport, building and industrial monitoring, entertainment, education, etc.

#### Scope and ambition

We have chosen some core technologies that we think are the most promising for many future applications in order to overcome the number of challenges we are facing for future ICs, in particular:

- High performance

- Low/very low static and dynamic power consumption

- Device scaling

- Low variability

- Affordable cost

Considering these challenges, the following nanodevices and technologies have been considered as very relevant for future Nanoscale FETs:

- FD (Fully Depleted) SOI (Silicon-On-Insulator) MOS-FET: for low power applications and low variability

- FinFET (or Trigate FET): for high performance and/or low power applications

- Nanowire FET: for high performance and low power applications and ultimate integration

- CNTFET/Carbon NanoTube FET: for very fast and possibly ultimately scaled transistors for logic applications, with self-assembly based fabrication

- NCFET/Negative Capacitance FET : for very low power application using steep subthreshold slope

- Non-charge-based Resistive Memories or alternative charge-based Memories: to replace charge-based memories using PCRAM (Phase Change RAM), RRAM (Resistive RAM using a nanofilament), MRAM (Magnetic RAM, especially STT/Spin Transfer Torque MRAM), or FeRAM or FeFET (using the polarization of a ferroelectric material)

- Sequential 3D integration: for increasing device integration (transistors, memories, sensors, etc.) using 3D stacking

- The roadmap also covers the future modelling and characterization tools needed for developing these future devices and technologies.

#### Main Concepts

- Nanowires

- FinFET

- FD-SOI

- Negative Capacitance FET (NCFET)

- Carbon Nanotubes (CNTFET)

- Memories, Concept 1 OxRAM:

- Memories, Concept 2 CBRAM

- Memories, Concept 3 PCM

- Memories, Concept 4 MRAM

- 3D sequential integration

- Reliability

#### Nanowires

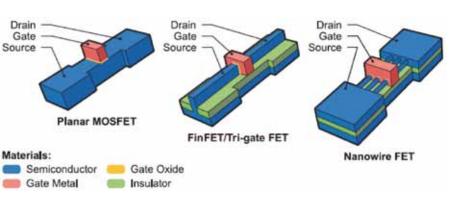

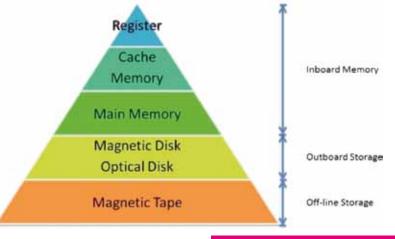

The evolution of MOSFETs is shown in Fig. II.1, starting from plane device to FinFET, ending by Nanowire FET, which could be the best device due to the following advantages:

- Advantageous carrier transport with optimized volume inversion: high transconductance gm and driving current I<sub>on</sub>

- Wrap-gate geometry and small nanowire diameter: large number of electrons, low output conductance g<sub>d</sub>, reduced short channel effects DIBL (Drain Induced Barrier Lowering) and charge sharing, low I<sub>nff</sub>.

#### Key research questions/issues

- What performance (I<sub>on</sub>, I<sub>off</sub>, gm, ft/f<sub>max</sub>, NF) can be achieved in different materials and geometries?

- How can different materials/geometries be manufactured at large scale?

- Evaluation of interface and dielectric quality from HCI and PBTI measurements

- Investigations of variability for 10 nm nanowire diameter/gate length transistors

- Circuit/technology co-design in 3D transistor architectures

- Integration strategies for III-V technology on a Si platform

#### Medium Term [+5 years]

Available data suggests that the best performance (lowest loff, highest lon, highest gm, etc) is obtained for Si, Ge, and III-V nanowires. Hybrid III-V/SiGe channel technology has been demonstrated as well as III-V gate stacks with Dit<10<sup>12</sup> cm<sup>-2</sup>. Transistor data is available for <10<sup>-15</sup> nm ln(GaAs) diameter

00000+

#### 000

- Current status includes first demonstrations of SRAM cells and first nanowire amplifiers designed in complex 3D geometries. A maturing technology will enable circuit implementation

- With current efforts on TMD materials synthesis, it is likely that the technology will mature and contribute to the roadmap

#### Application needs & Impact for Europe

Long Term [+10 years]

- Extend the roadmap for CMOS scaling based on improved electrostatic control and increased drive current

- Meeting the low-power demand for IoT applications

- Enhance the CMOS RF-properties by (III-V) materials integration

- Increase performance in mixed-domain by increase in f/f<sub>max</sub>

- Provide opportunity for efficient mmWave front-ends combined with high-speed digital logic

- Electrostatic control provided by nanowires/nanosheets critical for TFET implementation

- Low power operation suitable for Neuromorphic computing and Quantum Technologies

#### Medium Term [+5 years]

- Tailoring of Si and Ge nanowire transistors to meet the demands of IoT.

- Introduction of hybrid III-V/Si(Ge) and/or all III-V technology for high-performance applications (both RF/mmWave and mixed-mode)

#### 00000+

Integration of high-speed logic and high-performance RF front-ends using III-V technology combined with CMOS and possible TFETs

Long Term [+10 years]

#### Technology and design challenges

- Challenges in terms of 3D processing in complex geometries at 10 nm Lg

- Evaluation and reduction of parasitics in 3D transistors at 10 nm Lg

- Understanding and reduction of thermal effects in 3D transistors at 10 nm Lg (heating, reliability ...)

- Strain engineering (processing, characterization etc) at the 10 nm length scale

- 3D vertical transistor stacking to reduce area (vertical/lateral channels)

- Strategies for co-integration of various types of transistors (Si, Ge, III-V, CNT) in manufacturable CMOS processes

- Transistor and circuit co-design and optimization in complex 3D structures

- Introduction of Ferroelectric gate stacks to boost Ion

#### Medium Term [+5 years]

- Maturing of the process technology for Si, Ge and III-V nanowires to meet the requirements of IoT and high-performance applications

- First demonstration of nanowire circuits with competitive/high performance

#### Long Term [+10 years]

- Circuit layout in complex 3D architectures with minimized parasitics

- Improved materials and process control of 2D materials

#### Other issues & challenges, interaction with other areas

- Nanowire transistors provide the electrostatic control required for TFETs

- The electrostatic control in nanowires and sheets will allow for reduction of off-state leakage to meet IoT requirements

- The high gm and self-gain make nanowire transistors promising for millimeter wave applications (connectivity)

- A selection between nanowires and FinFETs is likely

- Technology suitable for Neuromorphic Computing and Quantum Technologies

#### Medium Term [+5 years]

• The technology development will follow point 1a-c

#### Long Term [+10 years]

• The technology development will follow point 1a-c

#### Nanowires

#### Competitive situation of Nanowires

Nanowire FET can be considered as the best FETs for the ultimate integration of CMOS devices with the best performance and lowest power consumption for the OX technology nodes.

#### Recommendations for Nanowires

Identify the best material and geometry options for logics (high-speed as well as low-power)

- Develop millimeter wave front-ends with III-V MOS-FETs (applications for communication, radar)

- Develop transistor/circuit co-design strategies for mixed and mmW applications

- Consider the 3D aspects of processing (stacking, vertical integrations etc)

- The electrostatics and heterostructure design options provided are beneficial for TFETs

#### Definition of FoMs or planned evolution

| FoM / Planned Evolution                                                                         | 2023                                                                                                                        | 2026                       | 2029                       | 2033                       |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|

| I <sub>on</sub><br>I <sub>off</sub><br>g <sub>m</sub><br>f <sub>t</sub> /f <sub>max</sub><br>NF | lon 650 μA/μm (normalized<br>to periphery)<br>> 3 mS/μm gm (normalized<br>to periphery)<br>< 1 nA/μm loff<br>> 500 GHz fmax | g <sub>m</sub> > 3.6 mS/μm | g <sub>m</sub> > 4.3 mW/μm | g <sub>m</sub> > 5.1 mS/µm |

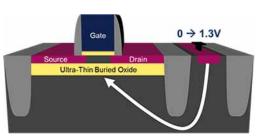

#### FD-SOI

8

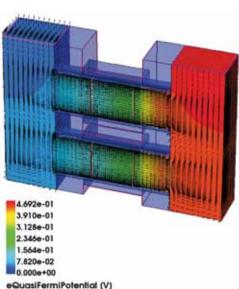

Fully Depleted Silicon On Insulator, or FD-SOI, is a planar process technology that relies on two primary innovations. First, an ultra-thin layer of insulator, called the buried oxide, is positioned on top of the base silicon. Then, a very thin silicon film implements the transistor channel. Thanks to its thinness, there is no need to dope the channel, thus making the transistor Fully Depleted. The combination of these two innovations is called "ultra-thin body and buried oxide Fully Depleted SOI" or UTBB-FD-SOI. FD-SOI technology enables control of the behavior of transistors not only through the gate, but also by polarizing the substrate underneath the device, similarly to the body bias available in Bulk technology. As the slowing of Moore's law signals the beginning of "Smart Everything", each FD-SOI process node can be a long lasting technology with differentiated options (RF, Mixed signal, Ultra Low Power, Embedded Memories, sensors...). The challenges and needs will be mainly focused on their ultra-low power possibilities to reduce as much as possible the supply voltage and improve the energy efficiency.

#### Competitive situation of FD-SOI

FD-SOI MOSFETs can be considered as the best FETs planar devices for low power applications, harsh environments (radiation, temperature), and they are also very interesting for analog and RF applications. While FinFET

is dedicated to high performance computing and high end application processor, FD-SOI is more dedicated to consumer applications, mid-range smartphones, IoT, wearables and sensors.

#### GLOBAL RECOMMENDATIONS for FD-SOI

From technological point of view, performances can be boosted also with breakthrough approaches like sSOI, monolithic 3D integration (e.g 28 nm/28 nm) or new materials without device scaling. From device architecture point of view, FD-SOI technology can suit 14 nm & 10 nm nodes and can be replaced by FinFET or Nanowires for 7 nm and below.

- Improve Performances with strain techniques & materials

- Develop differentiated options (RF, Embedded Memories, Imaging or sensors) on FD-SOI (applications for automotive, IoT, smart sensors...)

- Integration of FD-SOI with NVM (like PCM, OXRAM, FeFET...)

- Develop ULP design (V $_{\rm d}{<}0{,}4$  V) for IoT market (wearable, medical. . .)

- FD-SOI and 3D integration can respond to future neuromorphic and quantum computing approaches

#### Definition of FoMs or planned evolution

| FoM / Planned Evolution            | 2023                                                      | 2026                                                      | 2029                                                        | 2033                                                          |

|------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------|

| I <sub>eff</sub> /I <sub>off</sub> | I <sub>eff</sub> 470/420 μΑ/μm @10 nA/μm I <sub>off</sub> | I <sub>eff</sub> 470/420 μΑ/μm @10 nA/μm I <sub>off</sub> | Differentiation through options                             | Differentiation through options                               |

| Variability (Avt)                  | < 1 mV.µm                                                 | < 0.9 mV.µm                                               | < 0.8mV.µm                                                  | < 0.8 mV.µm                                                   |

| V <sub>dd</sub> (logic)            | < 0,7 V                                                   | < 0,65 V                                                  | < 0,6 V                                                     | < 0,6 V                                                       |

| Subthreshold slope                 | < 70 mV/dec                                               | < 65 mV/dec                                               | < 65 mV/dec<br>Introduction of sub-60mV/dec<br>technologies | < 60 mV/dec<br>Introduction of sub-60mV/dec tech-<br>nologies |

#### FD-SOI

0

| Key research questions/issues                                                                                                         | Medium Term [+5 years]                                    | 0000+               | Long Term [+10 years]                                   | 00000+<br>00000    |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------|---------------------------------------------------------|--------------------|

| <ul> <li>Improving performances for sub-14 nm nodes (strain</li> </ul>                                                                | <ul> <li>Introduction of dual stressors</li> </ul>        |                     | <ul> <li>More efficient dual stressors</li> </ul>       |                    |

| technologies for Higher drive current)                                                                                                | <ul> <li>on sSOI wafers</li> </ul>                        |                     | <ul> <li>on sSOI wafers</li> </ul>                      |                    |

| Structure evolution (Si & BOX thickness reduction chal-                                                                               | • T <sub>si</sub> <6 nm                                   |                     | • T <sub>si</sub> <5 nm                                 |                    |

|                                                                                                                                       | • T <sub>box</sub> <15 nm                                 |                     | • T <sub>box</sub> <10 nm                               |                    |

| <ul> <li>Evolution of planar FD-SOI to multi-gate structure (na-<br/>no-sheet) with at least 2 conductive channels</li> </ul>         | Development of planar nanosheet dev                       | vices (2 channels)  | More than 3 channels (multi stack                       | ·                  |

|                                                                                                                                       | • ULP IoT dedicated design $V_d < 0.5 V$                  |                     | • ULP IoT dedicated design V <sub>d</sub> <0,4          |                    |

| V OI) and sequential 3D integration                                                                                                   | <ul> <li>sSOI, SiGeOI with high Ge content, se</li> </ul> |                     | <ul> <li>sequential 3D sSOI / GeOI / III-V-O</li> </ul> |                    |

| controller applications / Automotive applications                                                                                     | Development of embedded flash men                         | nories (PCRAM,)     | New flash memories, innovative se                       | elector device     |

|                                                                                                                                       | <ul> <li>Development of FeFET for NVM</li> </ul>          |                     | <ul> <li>FeFET for NVM</li> </ul>                       |                    |

| • Electrical characterization of small scale devices (transport, capacitances, local strain impact)                                   | New techniques for short devices tran<br>zation           | nsport characteri-  | Evolution to Ballistic transport                        |                    |

| Application needs & Impact for Europe                                                                                                 | Medium Term [+5 years]                                    | 00000+              | Long Term [+10 years]                                   | 00000+<br>00000    |

| <ul> <li>low power applications</li> </ul>                                                                                            | Consumer, IoT, Automotive                                 |                     | • Automotive smart sensors / imagir                     | ng computing       |

|                                                                                                                                       | Application to wearable devices                           |                     | Application to medical devices                          |                    |

| Harsh environment resistant devices                                                                                                   | Spatial applications                                      |                     | <ul> <li>Spatial applications</li> </ul>                |                    |

| <ul> <li>FD-SOI Logic &amp; embedded flash memories for micro-<br/>controller applications / Automotive applications</li> </ul>       | Automotive, IoT                                           |                     | Automotive, IoT                                         |                    |

| integration with bipolar devices for high speed devices                                                                               | High speed Datacom                                        |                     | High speed Datacom                                      |                    |

|                                                                                                                                       | Concept of new sensors with FD-SOI                        | (Imaging, pH sen-   | <ul> <li>Applications to integrated and low</li> </ul>  | power Gas sensing  |

| SOI design for sensing)                                                                                                               | sing, gas sensing)                                        |                     | biosensing, Autonomous Imaging                          |                    |

| tum devices – eg: Qbit)                                                                                                               | Development of Quantum devices                            |                     | Development of Quantum systems                          |                    |

| <ul> <li>FD-SOI for neuromorphic circuits design challenges</li> </ul>                                                                | 3D integration for neuromorphic design                    | gns for processors  | 3D integration for neuromorphic d                       | esigns             |

| Fechnology and design challenges                                                                                                      | Medium Term [+5 years]                                    | 00000+              | Long Term [+10 years]                                   | 00000+<br>00000    |

| <ul> <li>Integration of Strain SOI substrates: processing of tensile<br/>strain for NMOS &amp; compressive strain for PMOS</li> </ul> | Local strain N & P MOS                                    |                     | • Local strain N & P MOS                                |                    |

| • Compatibility with flash memories process (as eg in BEOL)                                                                           | • Reliable and energy efficient embedde                   | ed memory           | Reliable and energy efficient embe                      | edded memory       |

| <ul> <li>FD-SOI design for ultra-low power (V<sub>dd</sub>&lt;0,4V)</li> </ul>                                                        | Subthreshold circuits                                     |                     | Circuits with sub-60 mV/dec devic                       |                    |

| <ul> <li>Evolution of FD-SOI co-integrated with Tunnel FET option</li> </ul>                                                          |                                                           | mV/dec devices      | • Development of solutions for sub-                     |                    |

| <ul> <li>Thermal management/self-heating mitigation with 3D in-<br/>tegration</li> </ul>                                              | -                                                         |                     | Low cost Passive Local cooling sol                      | ution              |

| • Integration with new materials (SiGe, High Ge content) and future III-V materials (logic applications)                              | High Ge conc. SiGeOI                                      |                     | 3D III-V OI circuits                                    |                    |

|                                                                                                                                       | Development of Co-integration of CM                       | OS with Si-photonic | Development of Co-integration of (                      | CMOS with Si-photo |

#### Other issues & challenges, interaction with other areas

\_ \_ \_

- Link with II.8: enabler for neuromorphic computing/ quantum computing

- Link with II.3-5: sensors+ CMOS co-integration

enabler

- Link with II.6: need for understanding system level benefit of 3D sequential options

- Link with II.7: development of strain silicon layers, low T processes, wafer bonding for new material on insulator, low temperature epi, gate stack materials/ interfaces development for low T for 3D technologies and new materials integration

#### FinFET

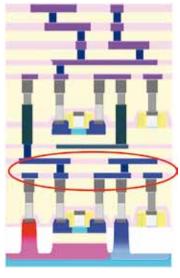

FinFETs are presently the most advanced nanodevices especially for high performance applications. They are using a trigate structure for improving the driving current and the control of electrostatic effects, as show below:

#### Competitive situation of FinFET

FinFET is the current workhorse device for advanced Si CMOS technologies and is current best option for the high performance space. It can also cover a part of the low power/low cost space.

#### Recommendations for FinFET

- Develop co-integration of different channel materials

- Develop low thermal cycle finFETs for sequential integration

- Develop low contact resistivity and high strain solutions

- Improve finFET analog performance

- Develop finFETs as devices for quantum computing

#### Key research questions/issues

- subthreshold slope control to less than 70mV/dec at very short gate length (<14 nm)</li>

- improved device performance (I<sub>on</sub>/I<sub>eff</sub> at given I<sub>off</sub>) while scaling the gate length and pitch

- control of parasitic capacitances at scaled dimensions

- Variability control at very scaled dimensions

#### Medium Term [+5 years]

- innovation needs to continue in the following areas: contact resistivity, conformal doping, dopant activation above solid solubility limit, low k or air spacer; HKMG scaling and multi-V<sub>1</sub>; high mobility channels; channel strain enhancement; integration of taller fins;

- understand under what conditions nanowires will outperform finFETs;

- Co-integration with other device architectures or between 2 channel materials

- 3D sequential integration with other devices

#### Long Term [+10 years]

- finfet is becoming a mature device architecture, on the longer term all optimization knobs may be already understood.

- 3D sequential integration with other devices

#### Application needs & Impact for Europe

- current workhorse device for Si CMOS technologies

- current best option for high performance space

- currently can cover part of the low power/low cost space

#### Medium Term [+5 years]

high performance space

#### Long Term [+10 years]

- can be considered for guantum computing as gbits

- Specialty sensors

high performance

#### Technology and design challenges

- No single device/material able to replace Si CMOS; Co-integration of finFET with other device architectures or between different channel materials will be key

- Improve finFET analog performance

#### *Medium Term [+5 years]*

- develop finFETs that can be processed at low T;

- develop finFETs that can withstand a long thermal cycle for 3D sequential integration;

- develop integration flows for multiple channel materials and strain(e.g. Si, SiGe, Ge, III-V on Si or SRB)

#### Long Term [+10 years]

00+

66666+

develop co-integration schemes between finFETs

and nanowires/nanosheets

#### Other issues & challenges, interaction with other areas

- manufacturing processes and integration will become very complex; working with increased aspect ratios will be key

- system level studies to decide what are the best devices to be co-integrated and in what way, for a given application

#### Medium Term [+5 years]

Manufacturing processes to be developed are same as in Key research questions/issues and Technology and design challenges

#### Long Term [+10 years]

- 00000

- Manufacturing processes to be developed are same as in Key research questions/issues and Technology and design challenges

## Definition of FoMs or planned evolution

| FoM / Planned Evolution            | 2023      | 2026      | 2029       | 2033       |

|------------------------------------|-----------|-----------|------------|------------|

| leff at fixed loff (normalized): 1 | 1.2       | 1.3       | 1.45       | 1.55       |

| CV/I (normalized): 1               | 0.75      | 0.7       | 0.55       | 0.5        |

| S (mV/dec): 65                     | 67        | 69        | 71         | 75         |

| min achievable I <sub>off</sub>    | <10 pA/um | <10 pA/um | <10 pA/um  | <10 pA/um  |

| Avt                                | <1 mV.um  | <1 mV.um  | <0.8 mV.um | <0.8 mV.um |

Advanced Logic/Memories

#### Negative Capacitance FET (NCFET)

11

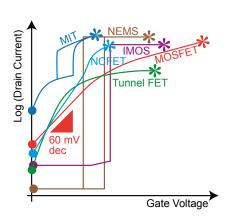

NCFETs ("Negative Capacitance" FETs) also have the potential to break the 60 mV/dec subthreshold slope limit but rely on another mechanism than TFETs. NCFETs have the same structure as MOSFETs except that a ferroelectric thin film is inserted between the dielectric and the gate. The ferroelectric material has a nonlinear polarization response to an applied electric field, with ionic dipoles switching when a coercive field Ec is reached. Measured in a metal-ferroelectric-metal stack, it shows hysteretic characteristic with residual polarization Pr (or -Pr) at zero applied field. Used in the transistor gate stack, the ferroelectric layer can lead to abrupt turn-on of the transistor from depletion to inversion during polarization switching, the polarized layer behaving as negative differential capacitance (i.e., opposite-polarity charge-electric field characteristic) during this transient. The polarization acts as a voltage shifter or a voltage amplifier, with the voltage seen by the transistor channel exceeding the applied gate voltage. If designed properly, this "negative capacitance" transient could possibly be stabilized by the series dielectric and depletion capacitance, leading to a hysteresis-free sub-60 mV/ dec operation.

Ferroelectricity was for a long time studied in perovskites, which are not compatible with CMOS processing. The emergence of Hafnium based ferroelectric layers since 2011 opens the door to standard CMOS compatibility and enables better scaling and integration to MOSFETs or FinFETs, therefore placing the NCFET as potential candidate for continuation of the scaling roadmap

#### Competitive situation of Negative Capacitance FET

A lot of research efforts are dedicated to the Negative Capacitance FETs. NCFET are plausible candidates to enter the logic scaling roadmap, in particular in the lower power range, where the steep slope allows to reduce Vdd while preserving the drive current.

#### Recommendations for Negative Capacitance FET

- Identify the maximum switching speed from dedicated RF measurements

- Identify from TCAD and modelling the optimal dimensions, in particular the coercive field and residual polarization for ultra scaled FETs

- Develop thin Hafnium based Ferroelectric layers with low coercive field and target polarization

- Develop understanding of the impact of traps and develop design and technology mitigation strategies.

- Develop compact models and design tools and evaluate the power-performance on real design contexts

- Investigate the impact of hysteresis at design level

- Investigate the scaling potential of the device

#### Other issues & challenges, interaction with other areas

- Suppression of trapping in the ferroelectric layer.

- Maintaining ferroelectric layer parameters during operation due to phase and temperature changes.

- Variability, reliability.

- Link with WP2: potential enabler for neuromorphic computing

- Link with WP6: development of strain silicon layers, low T processes, gate stack materials/interfaces development

#### Medium Term [+5 years] ••••+

## Long Term [+10 years]

#### Key research questions/issues

- Speed: what is the minimum FE layer polarization switching speed. Critical question for applications in logic circuit as it determines the maximum frequency of operation.

- Maximum frequency reported in literature ranges from ms to ps.

- Expected SS improvement over equivalent MOSFET or FinFET and benefit at circuit level.

- Proof that hysteresis free and sub-60 mV/dec operation are possible (stabilized capacitance behavior). If

not, is it possible to use it with hysteresis and what is the impact on circuit (active power, speed, variability).

- Limit of drive current: Although polarization amplifies the gate voltage and improves SS, the equivalent oxide thickness (EOT) is increased by the FE layer thickness compared to MOSFETs, this might lead to reduced lon in the high performance range.

#### Application needs & Impact for Europe

- NCFET is a potential candidate to continue the logic scaling roadmap if included in FinFET gate stacks at

aggressive nodes. It could improve the lon/loff ratio from low power to standard Vt flavors, and allow reducing V<sub>dd</sub> while preserving performance. Compared to FinFETs, its weaker design space is the high performance at high Vdd range.

- NCFET could also be a candidate to expand technologies at more relaxed dimensions such as in SOI and bulk planar 28 nm to 65 nm nodes, by improving performance and reducing power without area scaling and at lower cost than aggressive nodes.

#### Technology and design challenges

- Fabrication of thin Hafnium based (in Hf<sub>x</sub>Zr<sub>1</sub>-<sub>x</sub>O<sub>2</sub> and HfAlO) ferroelectric layers. Challenges of ferroelectric phase formation: strain, doping and anneal effect on Orthorhombic fraction, polarization barrier, crystallization. Experiment supported by ab-initio studies.

- Identification of the adapted coercive field and residual polarization for logic application and the feasibility to

obtain them in fabricated layers : Ec need to be lower than in FE memories while Pr needs to be sufficient

but designed according to the transistor available free charge.

- Capacitance matching: the FE layer, the oxide/interface dielectric and the depletion capacitance have to be

properly designed (capacitance matching) to have FE switching in depletion and to reduce the hysteresis.

- -• Polarization switching dynamics and frequency limit: understanding nucleation and domain wall propagation.

- Multi-domain or uni-domain ferroelectric layers : need and feasibility to make FE-layers with uni-domain nucleation.

- -• Impact of depolarization field: need and drawbacks of the depolarization.

- Footprint and scaling challenges: 2D field distribution, gate length versus gate stack scaling, ultimate FE scaling.

#### Definition of FoMs or planned evolution

| FoM / Planned Evolution | Device level metrics                           | Circuit metrics                                                                      |

|-------------------------|------------------------------------------------|--------------------------------------------------------------------------------------|

| to plan FoMs evolution, | <b>o</b> , , , , , , , , , , , , , , , , , , , | Logic active power consumption due to hysteresis.<br>SRAM stability with hysteresis. |

#### Carbon Nanotubes (CNTFET)

12

Carbon nanotubes (CNTs) are hollow cylinders composed of one or more concentric layers of carbon atoms in a honeycomb lattice arrangement, with a typical diameter of 1–2 nm. Depending on the arrangement of the carbon atoms, the CNTs can be either metallic or semiconducting, and are considered both for interconnect or as field effect transistors (FETs). The main expected benefits as field effect transistors over Silicon based devices are the following:

- The low-field mobility is very high in carbon nanotubes, much higher than in any other materials. This is due to the extreme reduction of scattering effects because there is no dangling bonds and surface states at the surface (perfect covalent carbon bonds), and because the transport is one dimensional. Ultimately this could lead to much higher drive current than in silicon based devices at same geometries, enabling higher speed, or reduction of the operating voltage and hence lower active power.

- The tube diameter is controlled by chemistry not by printing, allowing to reduce the body dimension beyond what is achievable for FinFETs and nanowires, that are defined by lithography. This ultra-scaled body leads to higher gate to channel coupling and better electrostatic control at short gate length. The small size also allows the fabrication of aligned arrays with high packing density.

- The intrinsic capacitance is a quantum capacitance related to the density of states and independent of electrostatics. The device capacitance could hence be much lower than the FinFETs gate to channel capacitances, reducing the switching energy.

#### Competitive situation of Carbon Nanotubes

The main research centers on CNTs are the university of Stanford and IBM. CNT have a lot of potential but the problem of source/drain contacts and the problem of variability due to metallic CNTs and to doping or ambipolarity need to be overcome and at the moment lower their chance to be competitive as field effect transistors. Their use in optical and biosensors applications is still promising.

Recommendations for Carbon Nanotubes

- Develop solutions to lower the Schottky barriers at source/drain

- Develop solutions to remove the metallic CNTs Develop faster growing process

- Develop circuit design strategies to deal with variability induced by m-CNTs and doping fluctuation

- Develop compact models and design tools and evaluate the power-performance on real design contexts taking into account the physics of the device (quantum capacitance) and its parasitics.

#### Definition of FoMs or planned evolution

#### FoM / Planned Evolution

Too early stage technology to plan FoMs evolution, The FoMs of Silicon MOSFETs (Ion, Ioff, gm, SS) apply. Percentage of failure and variability due the metallic CNTs and bad orientation (failed growth)

#### Other issues & challenges, interaction with other areas

- II.3, II.4 and II.5 functional diversification

- II.6 heterogeneous integration

#### Medium Term [+5 years] ••••+

Long Term [+10 years]

#### Key research questions/issues

- Metallic CNTs: CNTs are grown by a catalytic process that lead to semiconductor CNTs but also metallic CNTs. These metallic CNTs create shorts and hence transistor failure.

- Although the intrinsic device has extremely high mobility, the intrinsic performance is hindered by the source/drain access, composed of quantum resistance (mismatch in number of states in CNT compared to electrodes), Schottky barriers at the metal/nanotube interface, and parasitics series resistance.

- Schottky barriers in a CNTFET is the main issue for performance, impacting the characteristics not only the 'on' state (similar to a series resistance), but also the 'off' state, degrading the efficiency of the gate to switch off the channel, hence the leakage current and the subthreshold slope.

- In a thin gate oxide CNTFET, both Schottky barriers can become thin enough to allow the injection of both carriers simultaneously, leading to undesired ambipolar behavior.

- Although the quantum capacitance is extremely low, the coupling capacitance between the CNT and the surrounding conductors become more and more important at scaled dimensions and could hinder the benefit of the low intrinsic capacitance.

#### Application needs & Impact for Europe

- Nanotubes offer theoretically the potential of very fast (THz) and ultimately scaled transistors for logic applications, with self-assembly based fabrication. The issues of the Schottky barriers and variability caused by metallic CNTs are however at the moment show stoppers. The fabrication process might be cheaper but is slower, which is also an issue.

- CNTs are potential candidates for future via and wire material in nano-scale VLSI circuits, eliminating electromigration reliability concerns as they can stand much higher current density than copper interconnects.

- Transistors with properly functionalized CNTs are already being used as sensitive and selective chemical and biosensors.

- CNT-based nano-light sources and detectors may allow intra-chip optical communications and individual molecule level spectroscopy. Further integration to include optics could lead to a unified electronic-optoelectronic technology.

#### Technology and design challenges

- Technology solutions have to be found to remove metallic CNTs, or logic circuit design solutions to deal with caused variability and failure.

- Contacts: size-independent contact schemes with low Schottky barrier heights have to be developed that

do not hinder the intrinsic benefit of the CNT transport.

- Solutions have to be found to screen the impact of the Schottky barrier on leakage. A solution is to use independent gates near source/drain and in the channel, but this will hinder gate scaling.

- Fabrication speed: non metallic catalysts are slow, metallic catalyst lead to possible metallic CNTs hence shorts and device variability.

- The growth direction of SWNTs on SiO<sub>2</sub>-Si substrates is difficult to control since SiO<sub>2</sub> is an amorphous material. Misaligned CNTs lead to variability and failure.

- Non CMOS compatible metals like Au, Ti, Pd and Al are used for the source and drain electrodes and should be replaced by CMOS compatible options.

- High variability due to doping fluctuation in the ultra-thin body if n/p devices are made by doping (non ambipolar device).

#### Memories

13

The stand-alone market is currently dominated and driven by 3D NAND-Flash. This seems to be the main path on the roadmap for the next >5 years, with very limited global actors sharing market quotas (Samsung and Intel/Micron). It is more fruitful to focus on emerging non-volatile memories (eNVM) that can become the next product for specific applications, ie SCM/Storage Class Memory and embedded memories for IoT, automotive, low power markets. Also neuromorphic applications are seen as promising on a longer time scale as new

ENVM are substantially represented by the non-charge based technologies, PCRAM, OxRAM, CBRAM, MRAM and FeFET.

potential applications are arising.

All these concepts struggle today to show a convincing potential for a product. The issues are quite similar for all of them, and can be summarized into three points: variability, retention at temperature and density. Various proofs of concept have been shown for each of those, and even a few products:

#### PCM (all standalone/storage class markets):

- SAMSUNG 64 MB, 65 nm (2010)

- Micron 128 MB, 45 nm (2011)

- Intel 32 GB, (2017)

#### RRAM (OxRAM and CBRAM)(consumer embedded):

- PANASONIC 64 KB, 180 nm (2013)

- Adesto 64 KB, 130 nm (2010)

#### STT-MRAM(all standalone market).

- Everspin 8 MB, 90 nm (2014)

- Avalanche Technologies 4 Mb 8 Mb (2016)

From a European perspective the stand-alone market looks far away and running at an increasing pace. Embedded market seems to be the only field where a fair competition is still possible. Automotive-driven applications and non-mainstream technologies as FD-SOI can create the substrate where emerging eNVM can grow.

Currently the need for new memory concepts is clear and strong, driving considerable efforts into research. Emerging eNVM however are far from being ready, and the amount of new concepts can lead to a risky energydispersive research work.

In the short-time horizon, the main view needs to focus on clarifying which technology has most potentials for success. It can be agreed that each eNVM needs to be refined with respect to given specification, but it is also clear that, for the time being, the lack of specifications is not the development bottleneck. Rather, emerging technologies are struggling to match in a strong and reliable way any specification. As the need for scalable embedded memory is quickly rising (nodes <=28 nm) within 5 years we must expect to see a reliable demonstrator. Intel 3DXpoint technology, based on emerging NVM, suited for SCM application is probably the closest concept, but in the eNVM horizon no product exists that can claim this role.

We focus on two main aspects. First to describe the market needs and the actual situation and secondly to present the actual candidates that are most likely to contend the role of next eNVM. Summarizing in short the many aspects that characterize the NVM is not an easy task, but that indeed reflex the complexity of the NVM technology segment. We will discuss 5 different concepts that are currently challenging in the research effort to provide enough specs for convincing the market. Surely the application is there!

#### II.1 Advanced Logic/Memories

II.1 Advanced Logic/Memories

#### Memories, Concept 1 - OxRAM

#### Key research questions/issues

- HRS distribution reduction

- Operation energy reduction

- Forming Voltage reduction

#### Medium Term [+5 years]

14

- 00000+

- Much research efforts already spent with average results. In 5 years OxRAM must convince or will die:

- Cell shrinkage and/or encapsulation techniques can be beneficial to control variability and need to be investigated. It looks hard to find new materials after extensive research, but dopants and material phases are still an open topic.

#### Long Term [+10 years]

HRS distributions tightly controlled. This can happen in 2 ways: 1. On known materials like HfO<sub>2</sub>, working on scaling, encapsulation, programming techniques, CF confinement; or 2. Changing material. This way seems less likely, because HRS spread looks to be intrinsic in the CF-like switching. At this horizon market must see more than a convincing production a niche market, some volume must be expected.

#### Application needs & Impact for Europe

#### Medium Term [+5 years]

00000+

Embedded memory or storage class memory. Need in automotive, µC for general purpose, consumer market, ...

#### Definition of FoMs or planned evolution

| FoM / Planned Evolution | 2023                                   | 2033                                   |

|-------------------------|----------------------------------------|----------------------------------------|

| BER                     | BER<1E-6 (w/0 ECC)                     | BER<1E-6 (w/0 ECC)                     |

| Endurance               | >1E5                                   | >1E6 (for SCM >1E10)                   |

| Retention               | 10Y@85C and soldering reflow compliant | 10Y@85C and soldering reflow compliant |

| Forming voltage         | <3 V                                   | <2 V                                   |

#### .

00+

Other issues and challenges, interaction with other areas

Need to confine CF. work on the cell encapsulation

New designs on system level can open new (niche)

However, crossbar will be necessary for density,

HRS broadening is the Challenge. New materials, new

programming schemes need to be investigated.

market. Ex: IoT (this can be a mainstream), neuro-

morphic, TCAM, NV-DRAM, memory computation...

Medium Term [+5 years]

need for BEOL access diode

Recommendations for OxRAM

and interfaces.

#### Key research questions/issues

Memories, Concept 2 - CBRAM

- HRS distribution reduction

- Endurance increase

- · Improve data retention

#### Medium Term [+5 years]

Specimens are on the market! New generation required and attended. Can CBRAM meet specs for SCM?

#### Long Term [+10 years]

666+

CBRAM has to improve data retention, to meet Flash standards (85C 10y) or 125C 10y for automotive. Endurance is less stringent for most applications, but 1E5 will be required.

#### Application needs & Impact for Europe

- Embedded: integration at scaled node <28 nm.</li>

Scaled SoC, automotive application (but spec need to be demonstrated). IoT, Security applications (embedded security)

- SCM:

- Applications on PC, tablet, phones, consumer markets, High speed computation (Fast boot), Recovery after power loss

- Computing in memory

#### Other issues & challenges, interaction with other areas

- Need to confine CF. work on the cell encapsulation and interfaces.

- New designs on system level can open new (niche) market. Ex: IoT (this can be a mainstream), neuromorphic, TCAM, NV-DRAM, memory computation...

- However, crossbar will be necessary for density, need for BEOL access diode

#### Medium Term [+5 years]

- 0000(

- Difficult to say, CBRAM and OxRAM have big challenges in the 5 years horizon already

#### Recommendations for CBRAM

Same as OxRAM plus a special focus on data retention, which is probably the most challenging topic for CBRAM. Since CBRAM are already available as sampling parts, the identification of applications and assessment of REAL specs is mandatory in the next few years. This technology exists in Europe (Altis) and need to be evaluated.

#### Definition of FoMs or planned evolution

| FoM / Planned Evolution | 2023                                   | 2033                                   |

|-------------------------|----------------------------------------|----------------------------------------|

| BER                     | BER<1E-6 (w/0 ECC)                     | BER<1E-6 (w/0 ECC)                     |

| Endurance               | >1E5                                   | >1E6 (for SCM >1E10)                   |

| Retention               | 10Y@85C and soldering reflow compliant | 10Y@85C and soldering reflow compliant |

| Forming voltage         | <3 V                                   | <2 V                                   |

#### Memories, Concept 3 - PCM

#### Key research questions/issues

- Improve data retention

- Confine material for energy reduction

#### Medium Term [+5 years]

15

#### 0000+

Specimens are on the market! New generation required and attended. Probably the most mature option. Need to be tested by customers.

#### Long Term [+10 years]

#### Scaling can be a great challenge. Research needs to be focused in that direction.

#### **Application needs & Impact for Europe**

#### Medium Term [+5 years]

- 0000+

- Embedded: integration at scaled node <28 nm. Scaled SoC, automotive application (but spec need to be demonstrated). IoT, Security applications (embedded security)

- SCM

- Applications on PC, tablet, phones, consumer markets. High speed computation (Fast boot), Recovery after power loss

- Computing in memory

#### Other issues & challenges, interaction with other areas

#### Medium Term [+5 years]

Need for cell thermal confinement GST etching required. 2 research axes: 1. Materials improvement for guicker write/erase and 2. Improvement for higher thermal stability (for embedded applications, 150 C automotive + 260 C 2' for soldering reflow)

Scalability at 1x nodes with thermal confinement looks as a main challenge.

#### Recommendations for PCM

Long Term [+10 years]

PCR is probably the most mature eNVM solution. Some specimens exist on market (see above), however customers are skeptical. This is probably due to a very conservative approach in the memory market, which is historically very prudent. This could then represent a potential for European industry, which could differentiate itself, investing more on PCR development.

PCM needs to progress on integration, necessary for GST patterning. In addition, material research needs to be continued to optimize data retention for scaled nodes. Demonstrating the possibility to scale PCM cell to nodes <<28 is mandatory, and possible axis research exist already (e.g. confined cells).

#### Memories, Concept 4 - MRAM

#### Key research questions/issues

- integration

- consumption

- scaling

#### Medium Term [+5 years]

Process is still a challenge due to etching of complex stacks. Scalability is also challenging. Need to work on design to reduce consumption and currents.

0000+

00000

00+

#### Long Term [+10 years]

Below 14 nm, a new cell structure is required. Increasing the number of interfaces to stabilize the magnetic polarization.

#### Application needs & Impact for Europe

#### *Medium Term [+5 years]*

- Embedded: integration at scaled node <28 nm.</li> Scaled SoC, automotive application (but spec need to be demonstrated). IoT, Security applications (embedded security)

- SCM: Applications on PC, tablet, phones, consumer markets, High speed computation (Fast boot), Recovery after power loss

- Computing in memory

#### Other issues & challenges, interaction with other areas

#### Medium Term [+5 years]

Main issues related to integration and COST. Some samples are available (mainly Everspin). Fab integration demonstration required. New tools required for integration (large Capex). Need to demonstrate enough magnetic immunity, reduce programming and reading currents by a factor 5-10. Products expected in 1-2y horizon!

#### Long Term [+10 years]

## 0000-

Integration of MRAM process in foundries needs to be assessed. Reduction of programming current required (10-100 pJ/bit can be a reasonable figure).

#### Recommendations for MRAM

MRAM are becoming extremely popular in these years. However, etching, thus integration, problems can be much harder to solve than expected. Plus, the high current consumption can be a serious drawback for real applications, in particular for IoT.

| Definition of FoMs or planned evolution |                                        |                                        |  |  |

|-----------------------------------------|----------------------------------------|----------------------------------------|--|--|

| FoM / Planned Evolution                 | 2023                                   | 2033                                   |  |  |

| BER                                     | BER<1E-6 (w/0 ECC)                     | BER<1E-6 (w/0 ECC)                     |  |  |

| Endurance                               | >1E5                                   | >1E6 (for SCM >1E10)                   |  |  |

| Retention                               | 10Y@85C and soldering reflow compliant | 10Y@85C and soldering reflow compliant |  |  |

| Forming voltage                         | <3 V                                   | <2 V                                   |  |  |

#### Definition of FoMs or planned evolution

| FoM / Planned Evolution | 2023                                   | 2033                                   |

|-------------------------|----------------------------------------|----------------------------------------|

| BER                     | BER<1E-6 (w/0 ECC)                     | BER<1E-6 (w/0 ECC)                     |

| Endurance               | >1E5                                   | >1E6 (for SCM >1E10)                   |

| Retention               | 10Y@85C and soldering reflow compliant | 10Y@85C and soldering reflow compliant |

| Forming voltage         | <3 V                                   | <2 V                                   |

#### Memories, Concept 5 - FeFET

#### Key research questions/issues

- Increase of  $\Delta V_{th}$

- Variability control

- Physics understanding

- 16

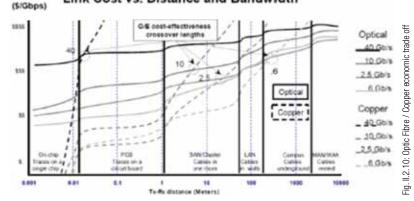

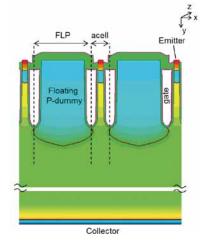

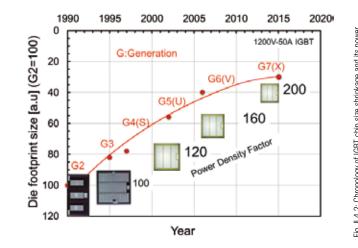

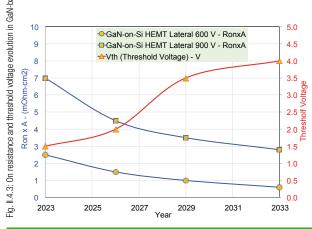

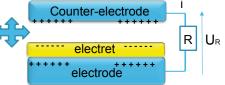

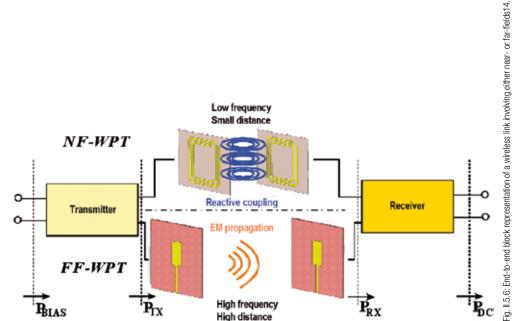

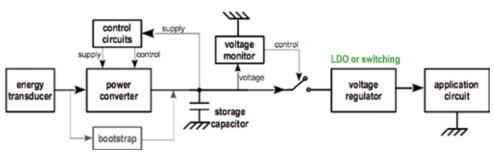

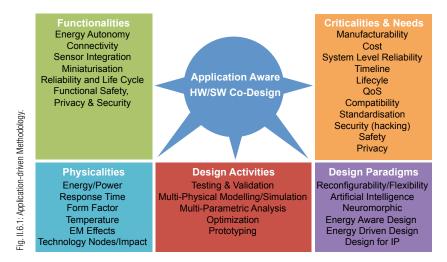

#### Medium Term [+5 years]