# THE NEXT SILICON FRONTIER

0

**EE TIMES 50TH ANNIVERSARY SPECIAL EDITION**

### CONTENTS

### **CHAPTER ONE:** THE FOUNDATION

- 6 1972: The Year Everything Changed

- **10** The Roots of Silicon Valley

- 10 Part 1: Founders, Legend, Legacy

- **17 Part 2:** Planar Technology, The Fairchildren

- 22 Part 3: Startup Fever and Venture Capital

- 29 Partner Content: Three Lessons from Valley's Analog History, and a Look Forward

- 36 A 50-Year History of the Microcontroller

- 40 Exclusive: An Interview with Carver Mead

- **46 Partner Content:** An Electronics Innovation Journey with EE Times

#### 50 CHAPTER TWO: THE SILICON GOLD RUSH

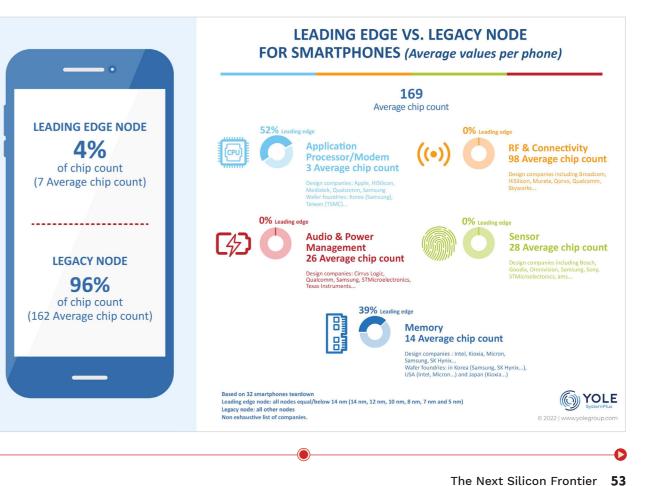

- 52 Silicon and the Semiconductor Industry: What Lies Ahead

- 56 What It Will Take to Keep Chip Scaling On-Track

- 60 China's EUV Conundrum in the Chip Cold War

- 63 Beyond Silicon: Exploring Compound Semiconductors

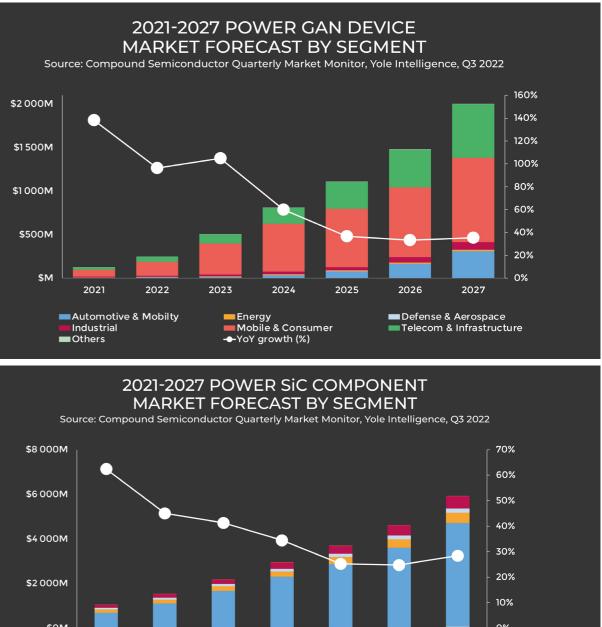

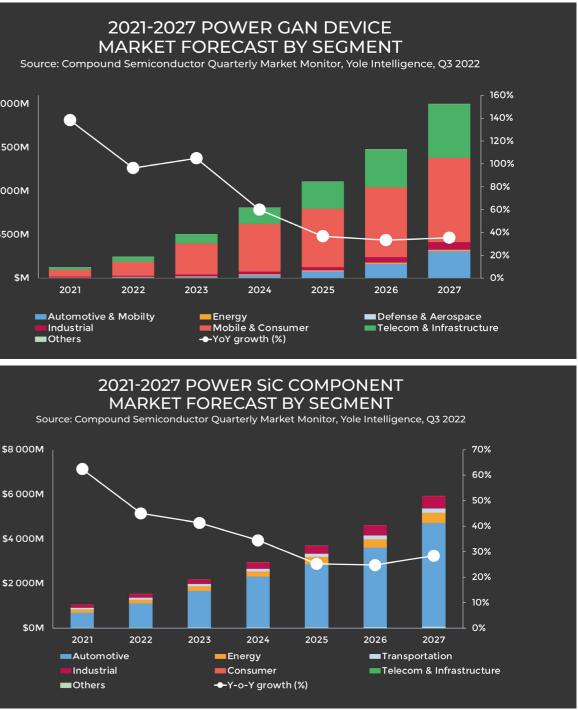

- 66 SiC and GaN: An Industry Driven by Different Engines

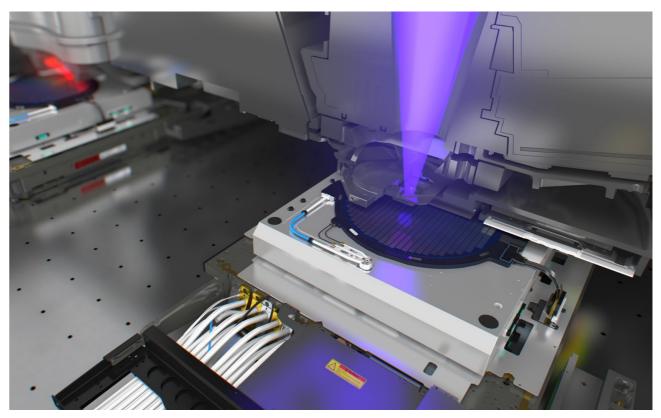

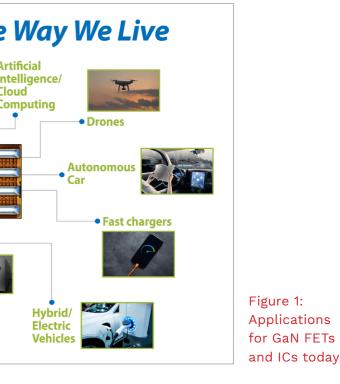

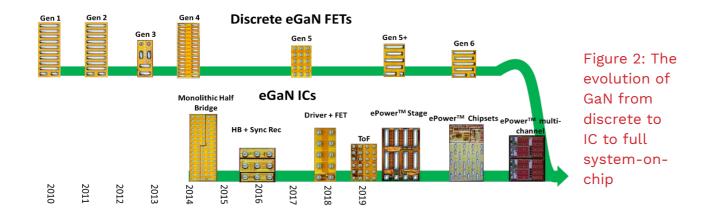

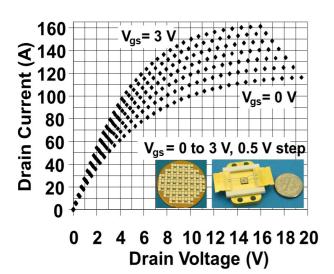

- 70 GaN's Evolution from Science Project Into Mainstream Power Semiconductor

- 73 Efficient SiC Power Devices Build on Silicon's Industry

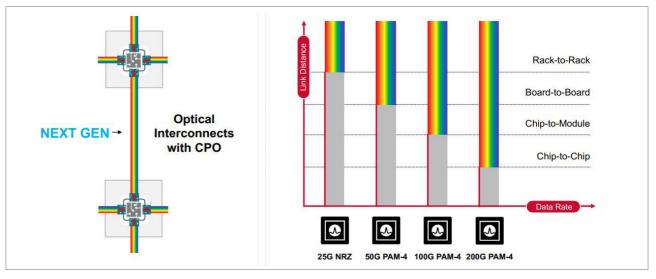

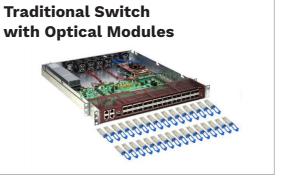

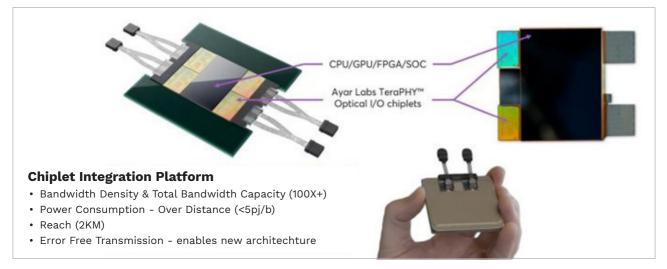

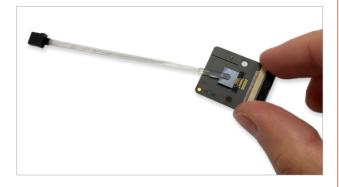

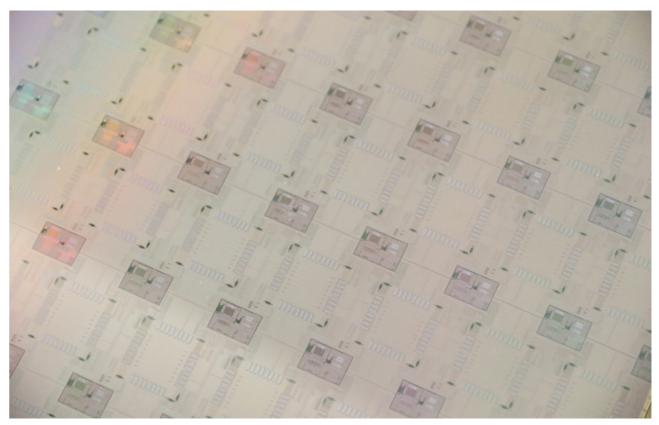

- 77 Silicon Photonics: Breaking the Interconnect

- 83 Partner Content: Rochester Keeps Business Moving: Then and Now

#### 88 CHAPTER THREE: THE NEXT SILICON FRONTIER

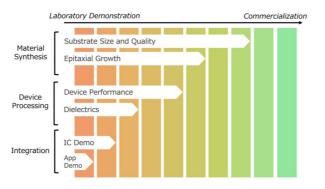

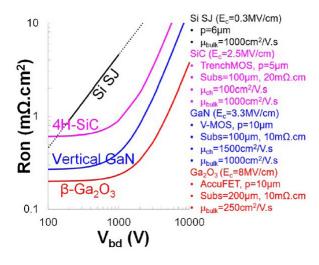

- 90 Gallium Oxide: A Next-Gen Semiconductor for Power Devices

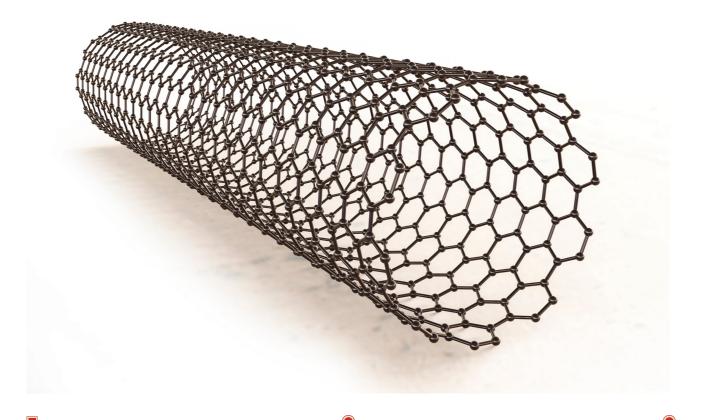

- 93 Nanotubes and 2D Materials: Change Agents for the Silicon Age?

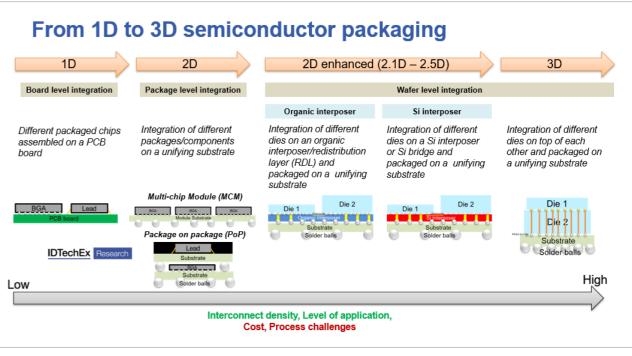

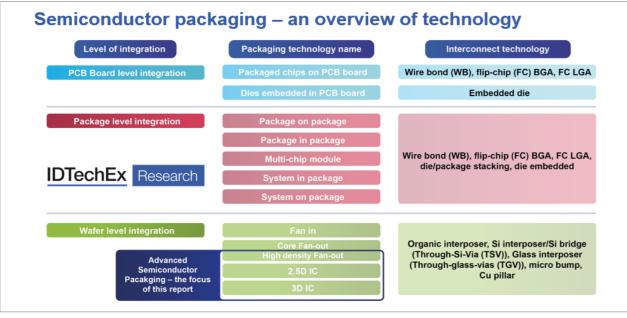

- 96 Advanced Semiconductor Packaging: From Technologies to Markets

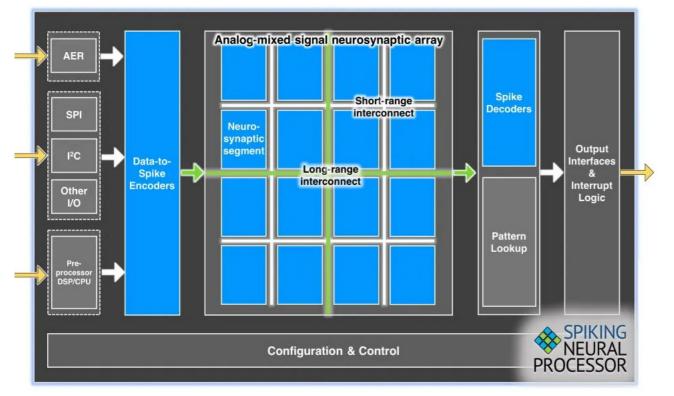

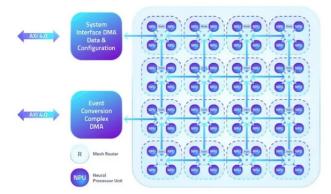

- 99 Digital Inspiration from the Analog Brain

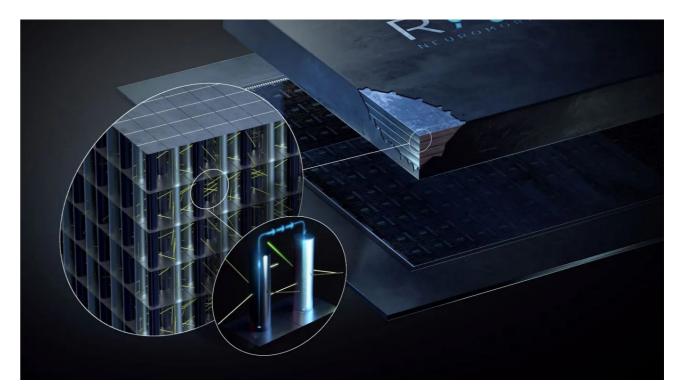

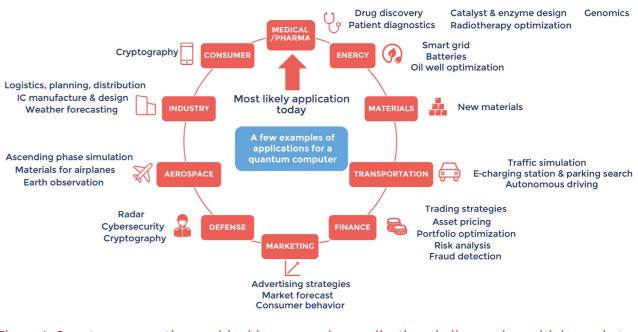

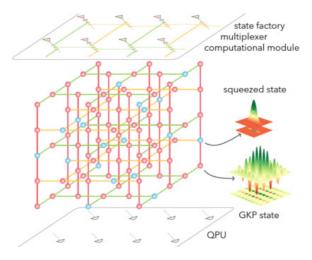

- 104 Going Beyond Moore's Law with Quantum Computing

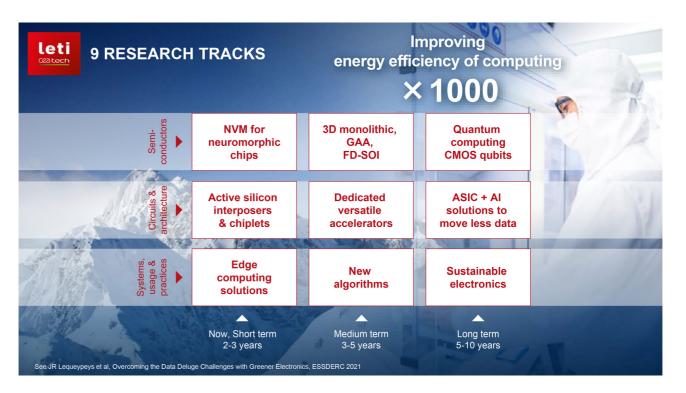

- **108** A Sustainable Path for Massive Data Generation

### FOREWORD

EE Times is 50, and to celebrate the milestone, we invite you to rewind, play, and fast-forward through electronic engineering times.

The integrated circuit was only six years old when Gordon Moore observed — nearly 60 years ago that the transistor count per silicon die area doubled roughly every year (which he later revised to every two years). Moore's Law transistor scaling pushed the semiconductor industry forward, bringing ever smaller, denser, and more powerful generations of chips to market that touched every facet of life and thereby changed society itself.

In 1971, Intel's first "micro-programmable computer on a chip," the 4004 microprocessor, held 2,300 transistors. By 2010, an Intel Core processor with a 32-nm processing die and second-generation high-k metal gate silicon technology held 560 million transistors. In 2021, IBM's 2-nm chip could fit up to 50 billion transistors while achieving 45% higher performance or 75% lower power consumption than state-of-the art 7-nm chips in production.

Node shrinking is getting even more extreme with TSMC's 1-nm process node, developed in collaboration with the Massachusetts Institute of Technology and the National University of Taiwan. But can we go beyond 1 nm? Convinced that "Moore's Law will not stop," imec is working on a sub-1-nm process, and its latest transistor roadmap extends to 2036. With industry partners ASML, TSMC, Intel, Samsung, and many others, imec is preparing to move beyond nanometer geometries to the angstrom era of semiconductors.

Despite the continued progress in traditional transistor scaling, the semiconductor industry has reached an inflection point. The demand for faster, smaller, smarter, and more energy-efficient chips calls for new design and manufacturing paradigms.

While it is still difficult to imagine a world without silicon, its physical limitations have shifted the focus to other semiconductor materials and compounds. Wide-bandgap semiconductors like silicon carbide and gallium nitride have received considerable attention, as they enable higher frequencies, higher voltages, and more complex electronic products than silicon.

To collectively prepare for the future, the "EE Times 50th Anniversary Special Edition: The Next Silicon Frontier" explores emerging themes like:

- Are carbon nanotubes, graphene, and other 2D materials change agents for the post-silicon age?

- Can photonics light the path to high-speed, energyefficient data processing?

- Is heterogeneous integration opening new possibilities in IC packaging?

- Will neuromorphic technologies pave the way for brain-like computers?

### **EE**Times D®

- How does quantum computing work, and why is it important?

- Is sustainable electronics attainable?

By asking and answering these questions, this eBook reflects 50 years of journalistic tradition at EE Times.

The name "Electronic Engineering Times" was first used on Sept. 11, 1972, according to the Official Gazette of the United States Patent and Trademark Office. In pursuit of the mission set forth by founder Gerard Leeds — connecting the global electronics industry — EE Times' reporters and editors quickly established the publication's voice, which echoed far beyond California's Silicon Valley to other meccas of electronics innovation, from Tel Aviv and Munich to Bangalore and Shanghai.

Over the decades, EE Times has endured by reinventing itself, just as the industry we cover has done. We have been agile, responsive, and innovative so that we would continue to meet our audience where they were. In the 1990s, EE Times was the first trade publication to go digital. In the early 2000s, we expanded globally, with a constellation of local-language websites in Asia and Europe. We developed eBooks in the 2010s and embraced books, podcasts, special projects, and virtual events in the 2020s.

What hasn't changed are our journalistic values and ethics. We still work to inform by going beyond the obvious, evaluating the different angles of a story, and contacting the right sources so that "the news" becomes a meaningful analysis of and for the industry. We tell the stories of the visionaries, pioneers, and innovators who have architected the digitization of society and who are preparing for its future. We forge intergenerational bonds and create intercultural connections to strengthen the global electronics community.

No engineer is an island. Innovations can only succeed if team members work toward common goals, if they meet a need or solve a problem, and if end users embrace them.

At EE Times, no editor is an island. Over the course of half a century, our organization would not have sailed through the still and the storms without business leadership and the hundreds of talented editors, copy editors, graphics designers, audience developers, doers, and go-getters who have populated our masthead.

EE Times' 50th-anniversary celebration is also yours, dear EE.

Together, we connect the dots between the past and the future. We connect science and society through technology.

Together, we write the history of the electronics industry.

- Anne-Françoise Pelé EDITOR-IN-CHIEF, EE TIMES EUROPE

The Next Silicon Frontier

3

# CHAPTER ONE: THE FOUNDATION

### 1972: THE YEAR EVERYTHING CHANGED

#### **BY BARBARA JORGENSEN**

EE Times D

"The Godfather" was playing in theaters everywhere, and "American Pie" was riding the FM airwaves. China was completely isolated from the West, and no one could imagine carrying a phone in their pocket. It was 1972, the year everything changed.

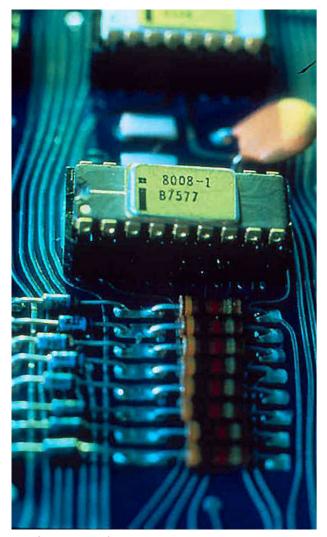

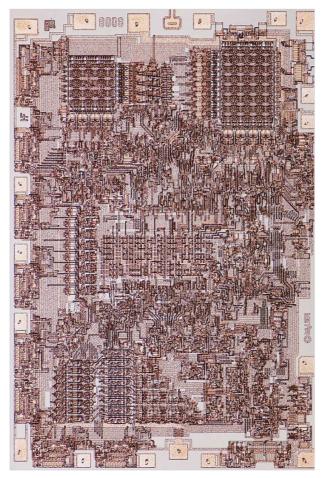

Intel's 8008 microprocessor (Source: Intel)

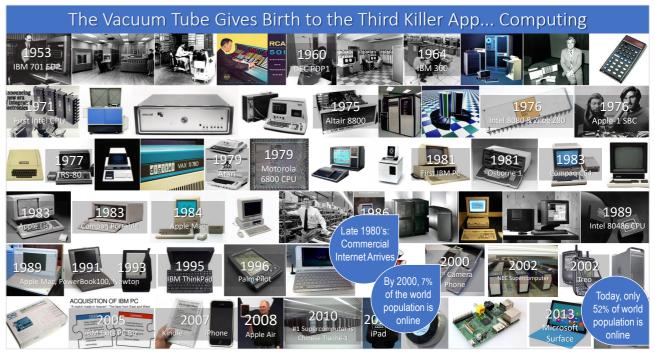

Hindsight being what it is, a series of seemingly unrelated events that year set the stage for the electronics industry we know today. U.S. President Richard Nixon visited China that year. Atari released the first-ever video game, "Pong." Intel introduced the 8008 processor, and the first epic rivalry for dominance in the computing market was just beginning.

"I think the early '70s were pivotal for the electronics industry," said Michael Knight, president of TTI Inc.'s Exponential Technology Group, SVP for corporate business development, and selfacknowledged high-tech history buff. "Gaming was the next killer app. TV and radio were the first killer apps driving electronic components, but back then, computing was a brute-force timesharing system. The early '70s set the stage for modern electronics. You had the first truly programmable microprocessor out of Intel."

The high-tech battleground at that time was handheld calculators, and the combatants were HP and Texas Instruments. As the story goes, HP co-founder Bill Hewlett issued a challenge to his engineers in 1971: Fit all of the features of their desktop scientific calculator into a package small enough for his shirt pocket. They did. The HP-35

(Source: TTI Inc.)

could not only add, subtract, multiply, and divide but compute trigonometric functions, logarithms, and exponents. It sold for \$395.

The following year, Texas Instruments countered with the SR-10. TI's calculator did not give values for trigonometric functions, but it cost only \$150.

Semiconductor technology was enabling smaller and faster devices. Intel's 8008 was the world's first 8-bit programmable microprocessor and only the second microprocessor from the chipmaker. It featured 50% more transistors and 8× the clock speed of its predecessor, the 4004, and it was capable of data/ character manipulation. Semiconductor historians credit the 8008 with cementing the future of microprocessor development and production as a business avenue, which paved the way for the modern computer age.

That release was illustrative of another technology battle that was in full swing: Japan's rise as an electronics powerhouse. Handheld calculators were introduced to the U.S. by Japanese companies Busicom (Nippon Calculating Machine Corp.) and Sharp (Hayakawa Electric). Chips in early Busicom calculators were made in the U.S. by Mostek and Intel, while Texas Instruments supplied ICs to American calculator competitor Bowmar.

## *By 1985, the solar-powered Sharp EL-345 calculator sold for \$5.95.*

Japanese companies and Japan's government, via its Ministry of International Trade and Industry (MITI), had been steadily investing in the nation's technology and manufacturing capabilities since the 1960s. Japan was already the price leader in consumer electronics, but until the early 1970s, quality had

7

been pretty shabby. Japan's automotive industry — another focus of the nation had adopted leading-edge practices such as lean manufacturing, which minimized inventory investment, and total quality management. Automakers had also begun to engage external suppliers, while the U.S. industry was still largely vertically integrated. These disciplines were easily transferrable to electronics.

Japan had built its edge in electronics by importing technology from other nations and then out-innovating the competition. The Sony Walkman, the VCR, and digital watches were all Japanese inventions. Two decades later, China would emerge as the low-cost option for electronics products and manufacturing services.

#### THE CHIPS

By 1972, Texas Instruments was accustomed to being top dog in the chip market. TI's Jack Kilby is credited with the invention of the integrated circuit as are Jean Hoerni and Robert Noyce of Fairchild Semiconductor — in the late 1950s. Kilby is usually credited with having developed the concept of integrating device and circuit elements onto a single silicon chip, while Noyce is given credit for having conceived the method for integrating the separate elements.

Intel's 8008 had been developed on a separate track from the 4004, and the newer MPU's higher transistor count, higher performance, and data-/charactermanipulation capabilities gave it broader market appeal. Developed for Busicom, the 4004 had 2,250 transistors and could

Intel's 8008 microprocessor, April 1972 (Source: Intel)

perform up to 90,000 operations per second in 4-bit chunks, but it could only handle arithmetic. The 8008 was a precursor to the x86 architecture, said TTI's Knight. "All these years later, the x86 is not a dead technology. Like MOSFETs, [the 8008 was] foundational technology."

Large-scale integration was also introduced in 1972. LSI enabled tremendous reductions in the cost. size, weight, and power consumption of components, along with increased speed and reliability. These features stemmed from the physical structure of the chip; more gates could be added without enlarging it - the personalization of computing had begun.

#### **GAMING**

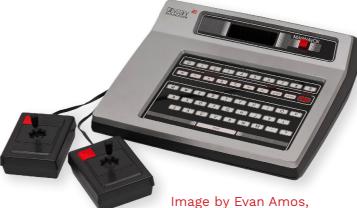

The first PC was still years away, but gaming was driving electronics innovation. Magnavox introduced the first gaming console, the Odyssey, in May 1972. The Odyssey had a number of removable circuit cards that switched between the built-in games. A few years later, with the Odyssey 2, each game could be customized, with its own background and foreground graphics, gameplay, scoring, and music. Game players could purchase a library of video games tailored to their interests.

The Odyssey 2 included a full alphanumeric membrane keyboard, intended for educational games, selecting options, or programming.

own work, CC BY-SA 3.0

"Gaming drove a bunch of innovations," said Knight. "It got people focused on on-board memory — the 8008 was programmable and could address 16 KB of memory — which was important for gaming. Somewhere along the line, the gaming industry made a mistake: It became more focused on software. Then there was this rebirth, thanks to Nintendo, and gaming went back to being the driver of chip technology. It gave birth to Nvidia and the GPU, which is now critical to autonomous driving."

### EE Times

By the mid-1970s, the first ROM cartridgebased consoles arrived, including the Atari Video Computer System (VCS). Coupled with rapid growth in arcade video games, including "Space Invaders" and "Pac-Man," the home-console market flourished.

#### THE RISE OF CHINA

Nixon's 1972 arrival in Beijing ended 25 years of no communication or diplomatic ties between China and the U.S. and was the key step in normalizing relations between the U.S. and the PRC.

"There is a lot of correlation between what happened in Japan and what's happening in China," said Knight. "Japan decided to move upstream in electronics, and the government got behind it and was very deliberate about enabling technology. That mantle got passed to China, which is on the same journey. From a government standpoint, China moved from being a second source to truly innovative with its own brands.

"Nixon going to China, which laid the foundation for its entry into the World Trade Organization [WTO], followed by electronics outsourcing, allowed China to start leveraging what [U.S. tech companies] were teaching them," he added. "It was a brilliant move on Nixon's part; he saw bringing China into the first world was the best way to defeat communism. Where we are today, regarding competitiveness with China, began with that decision."

Barbara Jorgensen is managing editor and co-founder of supply chain publication EPSNews.

### THE ROOTS OF SILICON VALLEY, PART I: FOUNDERS, LEGEND, LEGACY

#### BY MALCOLM PENN

EE Times 5

As part of our EE Times 50th Anniversary Special, this three-part series looks at the 74-year history of Silicon Valley, including how it came to be; why the captains of the nascent industry set up shop in California; and the legacy of William Shockley Jr., Fairchild, and the "Fairchildren" who laid much of the foundation for the semiconductor industry we know today. Part 1 considers the birth of the transistor, how Shockley ended up in Silicon Valley, the origins of Fairchild Semiconductor, how the pioneering startup was funded, and what eventually happened to Shockley.

#### WILLIAM SHOCKLEY JR. AND THE BIRTH OF THE TRANSISTOR

The transistor was successfully demonstrated on Dec. 23, 1947, at Bell Laboratories (Murray Hill, New Jersey), the research arm of American Telephone and Telegraph Co. The three Bell researchers credited with its invention were William "Bill" Shockley Jr.; John Bardeen, the department head and group leader; and Walter Brattain. Shockley continued to work on development at Bell Labs until 1955 when, having foreseen the transistor's potential and looking to work for more than a salary, he quit to set up the world's first semiconductor company, becoming a de facto industry father.

Shockley was born in London on Feb. 13, 1910, the son of William Hillman Shockley, a mining engineer born in Massachusetts, and his wife, Mary (née Bradford), who had also been engaged in mining as a deputy mineral surveyor in Nevada.

The family returned to the United States in 1913, setting up home in Palo Alto, California, when Mary joined the Mining Engineering Department faculty at Stanford University. But for this twist of fate — given that both Shockley's parents were mining engineers — the family could have instead settled in Colorado, Nevada, or West Virginia.

William Jr. earned his B.S. degree at the California Institute of Technology (CalTech) in 1932 before moving to the East Coast to study at the Massachusetts Institute of Technology (MIT) under J.C. Slater. He obtained his Ph.D. there in 1936, submitting a thesis on the energy band structure of sodium chloride, and joined Bell Telephone Laboratories, where he remained until his resignation in 1955.

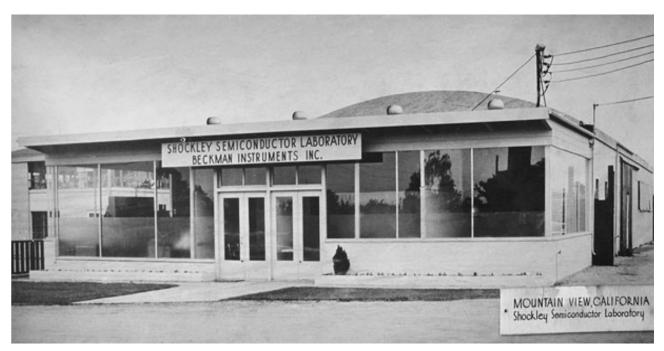

Shockley Semi-Conductor Laboratory (Source: Arnold and Mabel Beckman Foundation)

Upon leaving Bell Labs, Shockley moved back to Palo Alto (where his ailing mother still resided), initially as a visiting professor at Stanford but with the vision to establish his own semiconductor company making transistors and fourlayer (Shockley) diodes. Had he decided instead to remain on the East Coast — close to Bell Labs, MIT, or IBM in Vermont — Silicon Valley might well have developed on the East Coast rather than the West Coast of the United States. The geographical difference almost certainly would have shaped an industry with a markedly different personality.

In Palo Alto, Shockley found a sponsor in Raytheon, a pioneer in what came to be known as electronic warfare. But Raytheon's support was short-lived. Undeterred, Shockley, who had been one of Arnold Beckman's students at CalTech, turned to him for advice on how to raise \$1 million in seed money. Beckman was an American chemist, inventor,

### EE Times 59

entrepreneur, founder, and CEO of the hugely successful Beckman Instruments — and now also a budding financier who believed that Shockley's new inventions would be beneficial to his own company. So rather than pass the opportunity to his competitors, he agreed to create and fund a laboratory on the condition that the lab would work to bring its discoveries to mass production within two years.

Beckman and Shockley signed a letter of intent to create the Shockley Semi-Conductor Laboratory (the hyphenation was then common practice) as a Beckman Instruments subsidiary under Shockley's direction. The new group would specialize in semiconductors, beginning with the automated production of diffused-base transistors. Shockley's original plan was to establish the laboratory in Palo Alto, close to his mother's home, but that changed when Fred Terman, provost at Stanford

University and central figure in the rise of Silicon Valley, offered him space in Stanford's new industrial park at 381 San Antonio Rd. in Mountain View. Beckman bought licenses on all necessary patents for \$25,000, and the company was launched in February 1956.

#### STANFORD SOWS THE SEEDS

The seeds for Stanford's high-tech relationship with industry were sewn much earlier. In 1936, Sigurd and Russell Varian — together with William Hansen, Russell's ex-college roommate and by then a professor at Stanford - approached David Webster, head of Stanford's Physics Department, for help in developing the Varian brothers' idea of using radio-based microwaves for aircraft detection in poor weather conditions and at night. Webster agreed to hire them to work at the university in exchange for lab space, supplies, and half the royalties from any patents they obtained. The group's work eventually

led to the August 1937 development of the klystron, subsequently adopted by Sperry, and the formation of Varian Associates in 1948.

In 1938, shortly after the klystron's development, Bill Hewlett and David Packard, who had graduated three years earlier with degrees in electrical engineering from Stanford University, formed Hewlett-Packard in a garage at 367 Addison Ave. in Palo Alto under the mentorship of Fred Terman. The garage is often referred to as the "Birthplace of Silicon Valley," understating the contributions of Terman and Stanford in creating the catalytic environment for Californian high-tech ventures, as well as the explosive role that Shockley Semiconductor would subsequently play. From a semiconductor perspective, 381 San Antonio Rd. in Mountain View, Shockley's address, is more appropriately the real birthplace of Silicon Valley, as recognized by IEEE.

#### SHOCKLEY SEMICONDUCTOR

Given his own prodigious IQ, Shockley embarked on an ambitious hiring campaign, seeking to employ the brightest scientists available - not just Ph.D.s, but Ph.D.s from the finest universities who were at the very top of their class - bringing together a veritable brain trust of brilliant engineers. The hiring process was not that straightforward, however; because most electronics-related companies and professionals at that time were based on the East Coast, Shockley's startup had to post ads in The New York Times and the New York Herald Tribune. Shockley initially tried to recruit from his Bell Lab peers, but knowing his reputation as a difficult manager, none would join him.

Early respondents included Sheldon Roberts of Dow Chemical, Robert Noyce of Philco, and Jay Last, a former intern of Beckman Instruments. Each was required to pass a psychological test, followed by an interview. Julius Blank, Gordon Moore, Last, Noyce, and

### AD4630-24 Easy to Use Simultaneous Sampling 2 MSPS SAR ADC with Industry-Leading Performance

Linearity is guaranteed at ±0.9 ppm.

ANALOG

AHEAD OF WHAT'S POSSIBLE™

- ► Easy Drive<sup>™</sup> inputs improve compatibility with companion circuitry.

- Flexi-SPI interface relaxes user interface timing requirements without compromising performance.

Learn more at analog.com/AD4630-24.

Roberts started working in the April–May timeframe, and Eugene Kleiner, Victor Grinich, and Jean Hoerni during the summer. By September 1956, the lab had 32 employees, including Shockley.

Though never medically diagnosed by psychiatrists, Shockley's state of mind has been characterized as paranoid or autistic. All phone calls were recorded, and staff were not allowed to share their results with each other - not exactly feasible, given that they all worked in a small building. At some point, Shockley sent the entire lab for a lie-detector test, although all refused. Shockley also lacked business experience and industrial management, unilaterally deciding that the lab would pursue an invention of his own — the four-layer diode — rather than develop the diffused silicon transistor that he and Beckman had agreed upon.

### "...SHOCKLEY'S STATE OF MIND HAS BEEN CHARACTERIZED AS PARANOID OR AUTISTIC."

Barely six months passed when discontent boiled over, prompting seven employees to voice their concerns to Arnold Beckman — not to get rid of Shockley but to put a more rational boss between him and them. Their request might well have been granted had Shockley's Nobel Prize not been announced in November 1956, extending Shockley's fame and inflated ego. Rather than rock the boat, Beckman chose not to interfere, instead telling the seven to keep their heads down. Future Intel founders Noyce and Moore stood on different sides of the argument, with Moore leading the dissidents and Noyce standing behind Shockley, struggling to resolve conflicts. Shockley considered Noyce his sole supporter, but the team started to disintegrate, starting with Jones, a technologist, who left in January 1957 because of a conflict between Grinich and Hoerni.

#### **ARTHUR ROCK INVESTS**

In March 1957, Kleiner, who was also beyond Shockley's suspicions, asked permission to attend an exhibition in Los Angeles. Instead, he flew to New York to seek investors for a new company that he and the six others were by now contemplating. Kleiner's father, an investment banker, introduced Eugene to his broker, who in turn introduced Kleiner to Arthur Rock at Hayden Stone & Co. The team's original idea was to join an existing company. Rock, already investing in new companies - what today would be called startups — together with Alfred Coyle, backed Kleiner's proposition of a sevenstrong, pre-packaged team, believing that trainees of a Nobel laureate were destined to succeed. Finding prospective investors, however, proved to be difficult, given the U.S. electronics industry was at that time concentrated on the East Coast. The California Group - as the seven became known — wanted to stay near Palo Alto. Rock presented the group to 35 prospective employers; all declined.

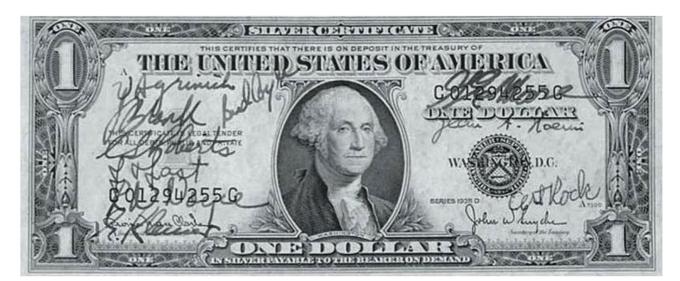

Dollar bills signed by each founding member were part of the contracts among the California Group, which formed the basis of Fairchild Semiconductor. (Source: Computer History Museum)

Lacking financial backing, the group led by Moore, as a last resort, presented Arnold Beckman with an ultimatum in May 1957: Solve the "Shockley problem" or they would leave. Moore proposed finding an academic position for Shockley, replacing him in the lab with a professional manager. Beckman again refused, believing that Shockley could still succeed — and shortly regretted that decision.

A month later, Beckman finally inserted a manager between Shockley and the team, but by then, it was too late, as the seven were now committed to leaving and embarking on Plan B — namely, creating their own startup. Recognizing they were followers, not leaders, the group persuaded the charismatic Noyce to join them. The now-expanded California Group met up with Rock and Coyle at the Hill Hotel in California. These 10 engineers became the core of a new company. Coyle, fond of ceremony, produced 10 \$1 bills and laid them carefully on the table. "Each of us should sign every bill," he said. "These dollar bills covered with

### EE Times 5

signatures would be our contracts with each other."

In August of that year, in a final throw of the funding dice, Rock and Coyle met with inventor and businessman Sherman Fairchild, founder of Fairchild Aircraft and Fairchild Camera and Instrument Co. The son of a wealthy entrepreneurial father who had made his fortune as an early investor in IBM, Fairchild was a bright and equally entrepreneurial engineer who had amassed a small fortune during World War II selling cameras for reconnaissance planes. Given that he had already developed an interest in semiconductors, Fairchild sent Rock to meet his deputy, Richard Hodgson. Risking his reputation, Hodgson accepted Rock's offer. Within weeks, paperwork and funding for the new company, Fairchild Semiconductor, had been completed.

The capital was divided into 1,325 shares, with each member of the California Group of eight receiving 100 shares, 225 shares going to Hayden Stone & Co., and

the remaining 300 shares held in reserve. Fairchild provided a loan of \$1.38 million and, to secure the loan, the eight gave Fairchild the voting rights on their shares with the option of buying them back at a fixed total price of \$3 million.

#### **'THE TRAITOROUS EIGHT'**

The eight left Shockley on Sept. 18, 1957, and Fairchild Semiconductor was born. While there is no documentary evidence, the group quickly became known as "The Traitorous Eight." Shockley never understood the reasons for their defection, considering it a betrayal, and allegedly never again spoke to Noyce or the others. With the help of a new team, Shockley brought his own diode to mass production the following year, but by then, time had been lost and competitors were already close to developing

integrated circuits. In April 1960, Beckman sold the unprofitable Shockley Labs to the Clevite Company, based in Waltham, Massachusetts, bringing his association with the semiconductor industry to an end.

On July 23, 1961, Shockley was seriously injured in a car crash and, after recovery, left the company and returned to teaching at Stanford. Four years later, Clevite was acquired by ITT. In 1969, ITT decided to move the lab to West Palm Beach, Florida, where it had an already-established semiconductor plant. When the staff refused to move, the lab ceased to exist.

Malcolm Penn is chairman, CEO, and founder of semiconductor industry analysis firm Future Horizons.

## THE ROOTS OF SILICON VALLEY, PART 2: PLANAR **TECHNOLOGY, THE** FAIRCHILDREN

#### BY MALCOLM PENN

Part 2 of this three-part series looks at the evolution of planar technology: the "family tree" of semiconductor startups that evolved from Fairchild (the "Fairchildren"), including Intel; and the competition with Texas Instruments.

#### FAIRCHILD SEMICONDUCTOR

Founded in intrigue, Fairchild set up shop on 844 E. Charleston Rd., on the border between Mountain View and Palo Alto, and went on to record a long history of innovation, producing some of the most significant technologies of the second half of the 20th century. It quickly grew to be among the top semiconductor industry leaders, spurred on by the successful development of the silicon planar transistor.

Transistors, however, were already presenting a new challenge, dubbed the "tyranny of numbers." If you wanted to make a simple flip-flop, it needed four transistors. About 10 wires were needed to connect them. Interconnecting two flip-flops required not only twice the number of transistors and wires but also four or five additional wires to connect the two devices. So four transistors needed 10 wires, eight needed 25, and 16 needed 60 to 70 wires. In other

- words, as the transistor count increased linearly, the number of connections grew exponentially, whereby the exponential was greater than one but less than two.

- While transistors were relatively easy to mass-produce, connections were much more difficult, as wires had to be soldered by hand and took up a lot of space. The industry's desire to build bigger and more complex systems was stymied by the difficulty in wiring everything together. To this point, few had paid much attention to wiring, but connections would soon become a potential showstopper, driving the need for the integrated circuit.

#### PLANAR TECHNOLOGY

In 1958, Jack Kilby of rival semiconductor company Texas Instruments demonstrated the ability to integrate a pair of transistors on a semiconductor substrate. Kilby's transistors were wire-bonded, however, leaving the connection problem

unresolved. That problem was solved by Bob Noyce, with the help of Jean Hoerni (who provided the technique) and Jay Last (who eventually made it work).

Hoerni had been working on a fix for reducing transistor defects. Defects were traced to unprotected transistor surfaces inside a package, allowing particles to contaminate and degrade the device over time. Hoerni's solution was to protect the transistor surface with a passivation, or protection, layer of silicon dioxide (SiO<sub>2</sub>), grown or deposited on top of the structure. Rather than deposit the emitter and base regions on top of the substrate, as with the current mesa process, Hoerni saw another way: If the surface was completely covered with SiO<sub>2</sub>, the emitter and base areas could then be selectively diffused. The net result was a much flatter surface, allowing for greater automation during production.

Planar technology, announced in January 1959, would become the second-mostimportant invention in the history of microelectronics — after the invention of the transistor — laying the foundation for future integrated circuits. At the time, the advance went virtually unnoticed, with the key exception of Noyce, who recognized that a glass layer was an insulator, providing a means for connecting wires laid on top and patterned like a printed-circuit board.

Noyce filed his patent in April 1959, triggering a legal battle between Texas Instruments and Fairchild (Kilby and Noyce remained friends, with high regard and respect for each other). Texas Instruments claimed that Kilby's patent claim — "electrically conducting material such as gold laid down on the insulating material to make the necessary connections" was a preexisting description of Noyce's patent claims and that Kilby had only used wire bonds as the quickest way to a prototype. Had this assertion been upheld, Noyce's later-dated patent would have been declared invalid.

### Texas Instruments lost the argument, both patents were declared valid, and the two companies reached a crosslicensing agreement.

Kilby was humble by nature, and even though his patent pre-dated Noyce's, he generously announced that both he and Noyce had invented the integrated circuit, contrary to the position of Texas Instruments' management.

In 1959, Sherman Fairchild exercised his right to purchase the founding members' shares, an event that turned former entrepreneurs and partners into ordinary employees, thereby undermining the company's team spirit and sowing the seeds of future friction.

Isolation was another big problem yet to be solved before integrated circuits could become a commercial reality. The problem was how to stop adjacent transistor interference. Noyce delegated this thorny problem to Last, who was running the R&D group. It was no easy task, taking some 18 months before the first working device was produced on Sept. 27, 1960.

#### TROUBLE AT FAIRCHILD

Development also met with strong internal resistance. Tom Bay, Fairchild's

vice president of marketing, accused Last of squandering resources. In November 1960, Bay demanded termination of the project, with the resultant savings allocated to transistor development. Moore refused to help, and Noyce declined to discuss the matter, leaving Last to fight the battle on his own. The conflict flared up barely a month after Fairchild announced the transition of its transistor production from mesa to planar technologies. Moore refused to credit this achievement to Hoerni, fanning the flames of the already-developing tensions among the eight founding partners.

Last continued to develop six more parts, but ongoing conflicts were the last straw. Flush with their planar and isolation process success, Last and Hoerni left Fairchild on Jan. 31, 1961, to launch Amelco in Mountain View, with financing from Teledyne Corp. arranged by Arthur Rock. Their plan was to develop ICs to support Teledyne's military business. Eugene Kleiner and Sheldon Roberts joined the pair a few weeks later. With this high-level defection, the eight founding members had been split into two groups.

Fairchild announced the world's first standard logic family of ICs, directcoupled transistor logic, in March 1961. The device was based on Hoerni and Last's resistor-transistor logic (RTL) planar

### EE Times Do

process under the  $\mu$ Logic trademark. The  $\mu$ L903 three-input NOR gate became the basic building block of the Project Apollo guidance computer. Designed by MIT and built by Raytheon, the lunar navigation computer required 5,000 devices and was the first major IC application. Miniaturization for space applications was driving early scaling.

Fairchild's lead, however, was shortlived. David Allison, Lionel Kattner, and others also left at around the same time as Hoerni and Last to launch Signetics (Signal Network Electronics). One year later, in 1962, the startup announced a much-improved, second-generation logic family, the SE100 Series diode-transistor logic (DTL). Fairchild quickly responded with its own DTL family, the 930 series, undercutting Signetics and rendering that company unable to compete against Fairchild's marketing juggernaut.

#### NE555 TIMER: MOST POPULAR IC EVER?

Signetics' most famous legacy part was the NE555 timer. Designed in 1971, the 555, along with the ubiquitous TTL 7400 quad two-input NAND gate, was probably the most popular IC ever sold. Signetics was acquired by Philips in 1975.

Early ICs were housed mainly in either TO-5 or TO-18 adapted metal can transistor packages. These worked fine for three-lead devices, but scaling them to provide more connections proved to be limiting, given that they could be made only so large and the radial leads packed only so tightly. Ten leads were about the practical limit and

Fairchild Semiconductor founders, 1957 (Source: Computer History Museum)

would not support the more complicated ICs in the pipeline. It fell to Fairchild's Don Forbes, Rex Rice, and Bryant "Buck" Rogers to provide a fix in 1964, via the invention of the now-familiar dual in-line package, the tiny oblong "millipedes" that would crawl across circuit boards for the next 40 years.

The packaging innovation stemmed from a ceramic flatpack design devised in 1962 by Yung Tao, a Texas Instruments engineer, as an industry standard for surface-mount ICs for the U.S. military. The concept was adapted for throughhole rather than surface mounting, with an eye toward ease of handling for electronics manufacturers and easier PCB layout design for delivering power to the ever-increasing number of ICs, routing their signals around the board. Another consideration was cost, given the growing consumer IC market. The 0.1-inch (2.54-mm) package pin spacing left plenty of room for PCB tracks to be routed between pins, and the 0.3-inch (7.62-mm) spacing between rows of pins left room for other tracks.

Fairchild launched its dual in-line package in 1965, originally in ceramic, but the package took off with a vengeance when Texas Instruments introduced a plastic resin version, driving the unit cost down dramatically. As a result of great design, low cost, and support for increasingly complex ICs, the plastic dual in-line package became the industry standard, with its basic 14-pin design extended to support more leads, up to 64 pins in a 0.6-inch-wide form factor, and more complex ICs. It was eventually surpassed by second-generation surface-mount devices in the late 2000s as chip complexity and pin count requirements surpassed the capability of dual-in-line packages.

With as many as 15,000 dies on a wafer, assembly and test now outweighed wafer fab costs — hence, the need to reduce labor costs as a matter of survival. After some early failed ventures — for example, in Shiprock, New Mexico, at a Navajo reservation — along with early attempts at automation, offshoring test and assembly to Asia proved successful, at least in the short term. Noyce, an investor in a small radio company in Hong Kong, suggested to Charlie Sporck that he and Jerry Levine scout the region.

They were attracted by the low labor cost, non-unionized facilities, Westerneducated technicians, good engineering schools, and tax incentives and other government subsidies. In 1963, Fairchild set up the industry's first East Asian assembly and test operation in a former shoe factory on the Kowloon side of Hong Kong. Other semiconductor manufacturers subsequently followed Fairchild to the region, primarily Malaysia.

#### FROM HOTEL CHAIN TO INTEL

Julius Blank, Victor Grinich, Moore, and Noyce stayed with Fairchild until 1968. In March of that year, Moore and Noyce decided to leave, turning to Rock for funding and launching NM Electronics in the summer of 1968. One year later, NM Electronics bought the naming rights from the hotel chain Intelco, thereby launching Intel Corp.

Grinich also left in 1968, first to teach at UC-Berkeley and Stanford, where he published the first comprehensive textbook on integrated circuits. But Grinich never lost the startup itch and quit academia in 1985 to co-found and run several startups, including Escort Memory Systems, developer of industrial RFID tags.

Blank, the last of The Eight, left Fairchild in 1969 to become a consultant to tech startups. Seeking a more hands-on role, he co-founded Xicor in 1978 to make E<sup>2</sup>PROMs.

As for the original four defectors, Hoerni headed Amelco until the summer of 1963, when, after a conflict with the Teledyne owners, he left for Union Carbide Electronics. In July 1967, supported by watch company Société Suisse pour l'Industrie Horlogère (SSIH), the predecessor of Swatch Group, Hoerni founded Intersil. The startup pioneered the market for low-power custom CMOS circuits, some of which were developed for Seiko. The combination kickstarted the Japanese digital watch industry.

Hoerni next launched the European version of Intersil, called Eurosil, financed in part by SSIH's desire to build a fab in Munich, not far from Swiss watch manufacturing.

### EE Times De

Eurosil was eventually sold to Diehl in late 1975. Hoerni left in 1980, returning to the West Coast to form Telmos. The startup produced semicustom products covering the linear interface between sensors to microprocessors and digital logic cores along with high-voltage, high-current drivers.

Last continued at Amelco, completing a 12-year tenure as VP of technology at Teledyne, Amelco's parent. In 1982, he founded Hillcrest Press, specializing in art books. Roberts also left to set up his own business and later served as a trustee at Rensselaer Polytechnic Institute.

That left just Kleiner, who departed to pursue a career financing the many early-stage companies springing up on the West Coast, teaming with Thomas Perkins, head of R&D at Hewlett-Packard, to form Kleiner Perkins. They opened an office on Sand Hill Road in Palo Alto, the locale that would become the home of U.S. venture capitalists. While Rock and Hayden Stone could arguably be credited with establishing the first venture capitalist firm, Kleiner Perkins was the first investor with a physical office in Silicon Valley. Kleiner Perkins would go on to fund Amazon, Compaq, Genentech, Intuit, Lotus, Macromedia, Netscape, Sun Microsystems, Symantec, and dozens of other companies.

As for today, Amelco — after numerous mergers, acquisitions, and rebrandings — no longer exists, but its IP portfolio survives, now owned by Microchip.

**Malcolm Penn** is chairman, CEO, and founder of semiconductor industry analysis firm Future Horizons.

### THE ROOTS OF SILICON VALLEY, PART 3: **STARTUP FEVER AND VENTURE CAPITAL**

#### BY MALCOLM PENN

The third and final part of our series explores the legacy of Silicon Valley as a result of the three key inventions that changed the world in the 1960s: the integrated circuit, startup fever, and venture capital.

### MELTING POT FOR THE FAIRCHILDREN

Sheldon Roberts, Eugene Kleiner, and Jean Hoerni's collective decision to leave and compete against Fairchild, just over three years after the company was founded, was the first of what would be many subsequent defections and spinouts. The "Fairchildren" would directly or indirectly create dozens of corporations, including Intel and AMD. Fairchild thus sowed the seeds of innovation across multiple companies in the region that would eventually become known as Silicon Valley.

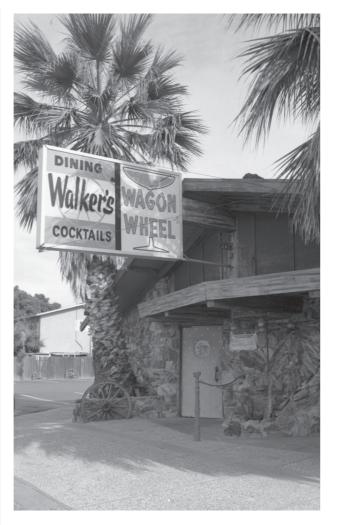

Local watering holes, restaurants, and other hot spots provided venues for Silicon Valley's "work hard, play hard" ethos, where industry folk gathered after work to drink, gossip, brag, trade war stories, talk shop, exchange ideas, change jobs, and develop new contacts. Key venues included the Wagon Wheel, Lion & Compass, and Ricky's, along with the Peppermill and the Sunnyvale Hilton.

Industry folk would meet, gossip, trade ideas, and change jobs at watering holes like the Wagon Wheel (pictured), Lion & Compass, and Ricky's. (Source: Computer History Museum) Stanford University, and particularly Fred Terman, also played a catalytic role, propelled by the engineering department chair's vision for academia to develop a new relationship with the science- and technology-based industries dependent on brainpower as their greatest asset. Terman further recognized the need to develop local industry, not just by building a community of interest between faculty and industry but also by encouraging new enterprises - what we would call startups today - to cluster around the university. To that end, Stanford provided intellectual property and office space, often rent-free other than the local property taxes.

While it is unclear who came up with the moniker "Silicon Valley," Don Hoefler, a technology reporter for the industry publication Electronic News, is often credited with popularizing the name in a 1971 column about the region's chip industry. Hoefler also promoted the area's innovative qualities and was one of the first writers to chronicle the Northern Californian technology industry as a community.

#### THE FAIRCHILD LEGACY

Throughout the first half of the 1960s, Fairchild was the undisputed semiconductor leader, forging ahead across all industry segments, be it design, technology, production, or sales. Early sales and marketing efforts were modest and military-oriented; that changed in 1961 when Robert Noyce and Tom Bay recruited a group of aggressive salesmen and marketing specialists, including W.J. "Jerry" Sanders III and Floyd Kvamme.

### EE Times De

The newcomers transformed Fairchild's sales and marketing departments into one of the industry's legends.

Among the pivotal moments was Fairchild's entry into the consumer TV market. Attracted by potential high volumes, Sanders wanted to replace the tube (valve) CRT driver with a transistor, but the target price was \$1.50. Transistors at that time were selling to the military for \$150. In what can only be regarded as a massive leap of faith, Noyce's instructions to Sanders were, "Go take the order, Jerry. We'll figure out how to do it later. Maybe we'll have to build it in Hong Kong and put it in plastic, but right now, let's just do it."

In 1963, Fairchild hired Robert Widlar to design analog operational amplifiers using Fairchild's digital IC process. Despite its unsuitability, Widlar, in partnership with process engineer Dave Talbert, succeeded in adapting the process to produce two revolutionary parts: the world's first operational amplifiers, the µA702 in 1964 and  $\mu$ A709 in 1965. With these two parts, Fairchild now dominated both the analog and digital IC markets, first with its µLogic RTL family and then with its 930 series DTL. In April 1965, Gordon Moore famously published his article "Cramming More Components onto Integrated Circuits" in Electronics. Later to be known as Moore's Law, it was basically an extrapolation of four plots on a graph showing IC transistor density over time.

Fairchild's digital technology lead was, however, being overtaken by Texas

Instruments. Having fallen behind in RTL and DTL, Fairchild's chief rival decided to copy Sylvania's ultra-high-performance (SHUL) transistor-transistor logic (TTL) circuit design, adapting it to its own process to counter the announcement of Fairchild's third-generation 9000 series TTL logic.

### "GO TAKE THE ORDER, JERRY. WE'LL FIGURE OUT HOW TO DO IT LATER."

Headed up by Stewart Carroll, Texas Instruments set up a "design factory" that could churn out several new designs a week, mostly by guessing the W/L ratios, laying out the circuits, correcting them if the prototypes did not work, and zeroing in on a specification that manufacturing could support. The design factory was supported by an optical photomask generator, as opposed to a manual rubylith layout, that could quickly create a photographic chip layout, as well as a "quick turn" fab line to churn out parts.

#### TTL DATA BOOK

To strengthen its attack, Texas Instruments masterminded a marketing coup by persuading other semiconductor companies to second-source its TTL rather than Fairchild's competing product. In this single masterly move, Texas Instruments established its 74 Series version of TTL as the de facto third-generation industry standard, leaving Sylvania's SHUL, Fairchild's 9000 Series, and other proprietary alternatives behind. It then proceeded to neutralize the entire second-source movement by providing every engineer with a copy of its ubiquitous orange book ("The TTL Data Book for Design Engineers"). Its twice-yearly "must attend" TTL seminars, not just in the U.S. but globally, were supported by an aggressive new product introduction program.

By always ensuring any bill of materials included at least one TTL part that was only available from Texas Instruments, the company was able to stay one step ahead of the competition and own the TTL market for the best part of 30 years, until standard logic eventually fell victim to the 1980s application-specific IC revolution.

In the meantime, starved of capex, Noyce's position on Fairchild's executive staff was consistently being undermined by Sherman Fairchild's corporate interference and his lack of support. The Fairchild management team was increasingly upset by Sherman's corporate focus on unprofitable ventures at the expense of the semiconductor division. The company suffered its ultimate humiliation in July 1967, when the semiconductor industry fell victim to the first of its cyclical recessions, during which the company lost money and was forced to concede its technology leadership to Texas Instruments.

Charles Sporck, Noyce's operations manager — often credited with running

the industry's tightest ship — left in early 1968 along with Pierre Lamond to join Widlar and Talbert at National Semiconductor. That triggered Noyce's and Moore's departures that same year — a

pivotal moment in the eventual demise of the firm. The collective exodus of Sporck, Noyce, and Moore, along with so many other executives, signaled the end of an era, prompting Sherman Fairchild to bring in a new management team led by C. Lester Hogan, then vice president of Motorola Semiconductor.

Of the eight original founders, only Julius Blank remained, although he, too, would be gone within a year.

#### HOGAN'S HEROES

Hogan's arrival, and the subsequent displacement of Fairchild managers, demoralized the company even further, prompting a further exodus of employees who would launch a host of new companies. Leading a group dubbed "Hogan's Heroes," the ultra-conservative Motorola executives immediately clashed with Sanders, Fairchild's flamboyant sales chief.

While initially slow to respond to the changing market under Sanders's direction, Fairchild had embarked on a strategy of leapfrogging Texas Instruments by focusing on more complex, large-scale parts with 30 gates or more, instead of simpler,

### EE Times De

small- and medium-scale devices under 30 gates — a strategy that was proving popular and successful with engineers. The move forced Texas Instruments to recognize the threat and copy all of Fairchild's 9300 Series parts under 74 series numbers (for example, the 9300 became the 74195 and the 9341 the 74181.)

Sanders's entire strategy collapsed, however, when Hogan capitulated to Ken Olsen, founder and CEO of Digital Equipment Corp. and a key Fairchild customer. Olsen wanted Fairchild to give up on its proprietary TTL technology and instead second-source Texas Instruments' 74 Series TTL. Against Sanders's wishes, Hogan agreed, signing the death warrant for Fairchild's TTL strategy. Sanders was, understandably, livid. "You've just killed the company, Ken," Sanders fumed.

Hogan's betrayal was the last straw for Sanders. He, together with a group of Fairchild engineers, quit to start Advanced Micro Devices. When Sanders was installed as president, one of his first moves was to establish the mantra: "People first, revenues and profits will follow." Sanders also gave every employee stock options in the new company, an innovation at the time.

Wilf Corrigan, who had moved with Hogan to Fairchild as director of Discrete Product Groups, succeeded Hogan as president and CEO in 1974. Fairchild continued to decline, however, dropping to sixth place in the semiconductor industry by the end of the decade.

In the summer of 1979, with the semiconductor market again riding high on its fourth year of successive double-digit growth, Fairchild fell victim to a hostile takeover bid from Gould, a major U.S. producer of electrical and electronic equipment, hell-bent on a diversification strategy.

Unable to fend off the buyout, Corrigan sought the best price for shareholders. Fairchild was eventually sold to Schlumberger, a French oil services industry company, for \$350 million, or \$66 per share (Gould went as high as \$57 per share). Schlumberger was unable to revive the deteriorating company, and it continued to lose money. Corrigan departed in February 1980, and once his non-compete clause expired, he and Rob Walker co-founded ASIC pioneer LSI Logic Corp. in 1981.

Schlumberger initially replaced Corrigan at Fairchild with one of its own managers, Tom Roberts, who unsuccessfully ran the firm like a heavy-equipment company. Two years later, in 1983, it recruited Donald W. Brooks, a Texas Instruments veteran, to reverse its decline. By then, Fairchild was a legend in trouble, lagging in leading-edge technologies and

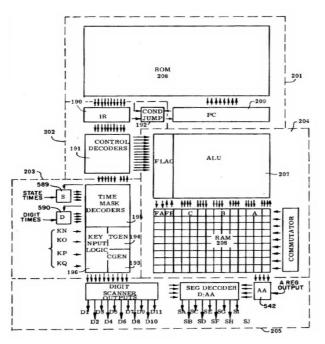

**GENESIS OF SILICON VALLEY** The Begats... 1947 Shockle Brattain **Bell Labs** Vm Shockley 1956 Bob Noyce Gordon Moore 1957 Transistor George Scalise Shockley Semi SIA Fairchild Bob Noyce MOS MPU Gordon Moore Jerry Sanders III Charlie Sporch Nilf Corrigan DRAM 1981 1961 959/67 1968 1969 Federico Faggin Bernard Peuto AMD Intel 2900/29K MPU National LSI Logic Signetics lar MPU 1974 1980 /ago 2014 Fujitsu Zilog Intersil Exar 1971 Vantis IDT Cypress Maxim Cirrus 19 PAL 1996-99 Flash EEPROM 2003 Logic 1982 Analog 1983 SRAM Linear Tech 1981 HP TI Sun Power PMC-Sierra 1984 Meanwhile ... Much later in SoCal ... Henry Samueli Back in Texas ... 54/74 Logic Back in Arizona .. Henry Nicholas II Calculators C Lester Hogan Natches TI MPUs DRAM Wilf Corrigan 1968 DRAM Pairgain Motorola TJ Rodgers LJ Sevin Fairchild Logic 1990 Mostek Cypress Broadcom 1972 1984 SRAM ON Semi Freescale Micron 1995 2000 2005 Avago 2015 NXP 2015

Key players in the creation of Silicon Valley's semiconductor ecosystem (Source: Jeff Software)

losing money, even as the rest of the semiconductor industry was booming.

The company was eventually sold to National Semiconductor in 1987 for onethird of the price paid by Schlumberger eight years earlier. With the Fairchild brand now dead, Brooks left, and the company was back in the hands of former Fairchild general manager Charlie Sporck. Kirk Pond became COO at National Semiconductor in 1994, where he led the successful management buyout in 1997. With the Fairchild name revived, Pond continued as president and CEO until 2005, when he became chairman, before retiring a year later in 2006.

Pond was succeeded by Mark Thompson until the company was acquired by ON Semiconductor (now onsemi) in September 2016. ON Semiconductor was the discrete, standard analog and logic device division spun out from Motorola's Semiconductor Components Group in 1999.

#### SILICON VALLEY LEGACY

On Feb. 14, 1956, Arnold O. Beckman and William B. Shockley announced to a luncheon audience of scientists, educators, and the press at San Francisco's St. Francis Hotel that they were founding Shockley Semiconductor Laboratory in Palo Alto. Not long thereafter, three critical advances in the 1960s — integrated circuits, startup fever, and venture capital — changed the world.

Perhaps these inventions would have happened somewhere else, at some other time, by somebody else. The fact that

they all occurred within a short space of time — in and around Palo Alto driven by the entrepreneurial spirit of the "Traitorous Eight" and many other key players, along with the startup ethos of Stanford University, made Silicon Valley unique in the history of technology.

But what if Shockley's parents had moved to Colorado, Nevada, or West Virginia to pursue their mining careers on their return to the U.S. rather than Palo Alto? Would Silicon Valley have developed instead in those places?

What if Shockley had chosen to set up Shockley Semiconductor on the East Coast, where there was an already-welldeveloped infrastructure, rather than Palo Alto, which had none? From the perspective of infrastructure, the East Coast was far better positioned to forge a Silicon Valley.

What if Terman hadn't had the foresight to develop a community of interest between Stanford's faculty and a fledgling industry, encouraging new enterprises to cluster around the university?

The Next Silicon Frontier 27

What if the Russians, Europeans, or Japanese had invented the integrated circuit first? Could Silicon Valley have sprung up in the USSR, Europe, or Tokyo instead?

What would the world look like today had any of these scenarios not unfolded?

Clearly, fate played a role in bringing Shockley and semiconductors to Palo Alto, but the West Coast proved a far more fertile environment for the risktaking spirit of the "Traitorous Eight" and their peers than the more risk-averse East Coast business and financial communities.

All eight of the original founders eventually left Fairchild and went on to become serial entrepreneurs, co-founding a wide variety of new startups, both in semiconductors and venture capital. They surrounded themselves with brilliant

engineers who also wanted to start new companies, prove themselves, and change the world — stoking the startup boom driven by Shockley Semiconductor as the embryo, Fairchild Semiconductor as the incubator, and the Palo Alto ecosystem as the catalyst.

The rest, as they say, is history.

Perhaps Walker, the co-founder of LSI Logic, best summed up the entrepreneurial spirit of the Valley, and the rise and fall of Fairchild, with this comment: "It's amazing what a few dedicated people can accomplish when they have clear goals and a minimum of corporate bullshit."

Malcolm Penn is chairman, CEO, and founder of semiconductor industry analysis firm Future Horizons.

#### PARTNER CONTENT

### THREE LESSONS FROM VALLEY'S ANALOG HISTORY, **AND A LOOK FORWARD**

**BY DAVID ANDEEN**, SENIOR DIRECTOR, BUSINESS DEVELOPMENT AND MARKETING, ANALOG DEVICES

#### LESSON I: STICK WITH YOUR PASSIONS

Energetic and freshly graduated from Stanford with an electrical engineering degree, Bob Reav had all the opportunities in the world. The burgeoning economic engine of Silicon Valley meant jobs. "When I graduated, I had a job offer from Intel to work on the 286 and a job offer from Intersil to work on A/D converters," recalled Reay, who today is vice president and Fellow, Power Products, at Analog Devices. "I decided to go to Intel because they were the big thing. Then the guys at Intersil called and said, 'Bob, do you like to windsurf?' I said yes. They said, 'Come and work for us; we'll buy you a windsurfer.' I said, 'Oh, really? Well, how about you throw in a roof rack and a wetsuit?' The next thing you know, I had been bribed by windsurf equipment and became an analog designer."

Thus launched Reay's amazing analog design career, one of many that connect the rich history of analog semiconductor innovation. At Intersil, Reay joined future Maxim leaders Tunç Doluca (CEO) and Pirooz Parvarandeh (CTO), both early in

their careers, developing A/D converter products and other core analog products that continue to provide revenue and innovation streams to this day.

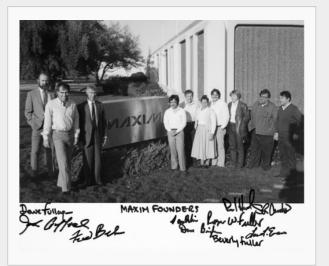

Maxim's founding team (from left): Dave Fullagar, Jack Gifford, Fred Beck, Sam Ochi, Dave Bingham, Beverly Fuller, Roger Fuller, Rich Hood, Lee Evans, Steve Combs

Intersil fits into Silicon Valley history in a unique way. Founded in 1967 by Jean Hoerni, Intersil's claim to fame is Hoerni's planar process, the exact foundation upon which semiconductor fabrication takes place today. "Back then, there was a tight connection between the process and the designer — the process was like another design tool," recalled Reay. The

nature of planar devices, such as the values of passive components, meant designers needed to redevelop classic analog circuits, which originally consisted of large discrete resistors and capacitors. At the time, and continuing to this day, demand for analog designers fueled the fate of companies across the industry.

The seeds of today's Analog Devices, the global leader in analog semiconductors, grew in many ways from Intersil. General Electric owned Intersil, which organizationally resided in the lighting division. The pairing seemed odd, especially to casual West Coast engineers, who periodically received visits from white-shirted East Coast executives. "At one point, Jack Welch came out to visit," said Reay. "They actually rolled out a red carpet for him!"

The boiling point developed with one of the analog industry's central figures: Jack Gifford, founder and first (and longtime) CEO of Maxim. At the time, the topic of stock options was a consistent issue with GE management, who did not grant them to other divisions. Employees at Intersil, conversely, viewed stock options as a fundamental component of compensation, the fuel and excitement of a startup, and the potential for riches. Gifford agreed to join Intersil only if he received stock options. The issue exploded when the two Jacks, Gifford and Welch, argued at a party and Gifford told Welch to "f--- off." Those who knew Gifford were not surprised. Welch didn't wait long to fire Gifford, who promptly responded by launching Maxim in 1983.

In founding Maxim, Gifford brought together some of the finest minds in analog, with the goal of creating an employee-owned company that put analog first.

Two years earlier, the genesis of Linear Technology, another legendary analog company, formed from National Semiconductor. National had long been the standard for an aggressive, innovative Silicon Valley company, with characters like Charlie Sporck, the hard-charging, cigar-toting CEO with the wry smile. Meetings regularly were punctuated by shouting and the pounding of fists on tables in what now seems like an odd way to keep the lines of communication open. But the culture worked for Silicon Valley. Bob Swanson, the founder and primary CEO of Linear Technology, left National with four brilliant colleagues: Bob Widlar, Bob Dobkin, Brian Hollins, and Brent Welling. The story goes that National became increasingly political, requiring Swanson, a VP at the time, to spend half his days justifying analog to the centralized teams, who believed that if a process worked for digital, it should work for analog, too. At one point, the analog product line yields dropped to zero because the production team had removed a critical die coat step.

After gathering the team to start Linear Technology, a few months went by before the company got moving. Swanson recalls the five spending their evenings shooting pool and drinking beer in his garage. Finally, one day, Welling asked, "Are we going to start a company or just drink beer and play pool every night?" With that, Swanson and the team took action. Linear sometimes gets referred to as "The House of Bob" — but not because of all the Bobs. Although Widlar and Dobkin are legends, Linear was the House of Bob Swanson.

On the other side of the country, Analog Devices was steadily building its own analog franchise. Reay remarked, "ADI always seemed more academic, and also more open" with technology and information. Around the time that Maxim and Linear Technology were just starting up, ADI was celebrating more than 15 years of existence and over a decade of operation as a public company.

Analog Devices founders Ray Strata (left) and Matthew Lorber

#### LESSON 2: DON'T BE AFRAID OF FAILURE

Reay's technical education began early. "My father was a math professor, so I grew up doing math problems at the dinner table," he recalled. "I had no idea that this wasn't normal until I actually got out of high school and met real people! I got a Radio Shack electronics kit while I was in high school. I started playing with that and building all sorts of circuits. It was fun, but [the kit] didn't really explain how [the circuits] worked.

"Dad bought us an Apple 2 computer, which came out after my freshman year in college," he continued. "That summer, my brother and I took apart the Apple 2 and decided to build a speech synthesizer for it. We bought this 40-pin DIP chip and built the card. We wrote all of this code, and we're finally getting it ready. As we plug in the card, smoke comes pouring out! So Dad walks by and says, 'OK, boys, what did you do?'

"We didn't have a lot of money at the time, so my dad made us do a failure analysis to find out what had happened. We finally figured out that we plugged the card in without turning off the power. The board we plugged in had these big bypass capacitors, so when you plugged it into the backplane, you had this big inrush of current. I'm telling you this because you can't let the fear of blowing stuff up stop you.

"You cannot be afraid of failure," Reay asserted. "Failure is part of the process."

Indeed, Silicon Valley and failure intertwine and connect uniquely and consistently. While the world celebrates technology breakthroughs, successful IPOs, and the winners of history, progress completely stalls without the many, many failures that precede any level of success. This truth holds even more for the analog industry. Dobkin once remarked that "an analog design engineer with 10 years of experience was more valuable than an engineer with five years

of experience, because he had made more mistakes."

The process of failure, and amazing success, for Silicon Valley begins with William Shockley, the inventor of the transistor, Nobel laureate, and founder of Shockley Semiconductor.

Reay recalled, "At Stanford, we had these dorm seminars where we'd invite Nobel laureates to come and talk to us. When I was an early undergrad, we had Bill Shockley come in and talk to us. Then we took him to lunch at the food service. It was really interesting to hear him talk about the early years of Silicon Valley, and even before, with the early work in semiconductor physics.

"The thing I can say is, it seemed to be this really exciting time when stuff was developed. Stuff that today you take for granted: simple things, like a planarized process or just integrated circuits or low-dropout [LDO] regulators. There are all these things that you think have been around forever, but they weren't around forever. There were a lot of fundamental breakthroughs going on."

While an amazing technologist who could spot talent and reportedly "see electrons," Shockley managed poorly and exhibited extreme paranoia. In 1957, frustrated with Shockley, the legendary "Traitorous Eight" — Gordon Moore, C. Sheldon Roberts, Eugene Kleiner, Robert Noyce, Victor Grinich, Julius Blank, Jean Hoerni, and Jay Last — all left Shockley. The group found funding and started Fairchild Semiconductor in Palo Alto, California. That seminal moment spawned the era of semiconductors, arguably the birth of Silicon Valley. A multitude of innovation, processes, products, and companies were formed from the seed of Fairchild, from the household-name semiconductor companies like Intel and AMD to companies pursuing other products, such as color TVs. A familiar Silicon Valley pattern emerged: Innovate, fail, succeed, and try again.

The characters in this story descend from Fairchild. Gifford worked at Fairchild, having been handpicked by Widlar to run the nascent linear circuit business. Gifford then co-founded AMD with Jerry Sanders in 1968. After conflict with Sanders, Gifford briefly went into farming before returning to semiconductors at Intersil. Swanson worked at Fairchild from 1963 to 1967, primarily in manufacturing and operations, before ultimately joining National.

The paths of Gifford and Swanson differ and coincide in many ways. Gifford grew up in Torrance, California, a baseball-playing West Coast native who attended UCLA and spent his life in California. Swanson, by contrast, hails from Wilmington, Massachusetts — the modern-day headquarters of Analog Devices, by coincidence — and spent time on both coasts, as well as stints in Scotland and Germany while at National. Despite these differences, the two shared a strong passion for technology, their companies, and, most importantly, getting the most out of their employees.

#### **LESSON 3: DIG DEEP**

"Swanson was a taskmaster," said Reay. "His genius was understanding where everyone's peak performance was. He would push each person to be their best — it's a different level for each person. We used to go into meetings where we knew there would be bullshit. We used to take bets to see how many questions it took Swanson to ferret out the bullshit. He would always figure it out. If you made stuff up, you were verbally killed. It was tough!"

Reay offered an example from his own experience: "In one particular instance, I had just come out with the LTC485. One of the issues was latch-up. When it gets zapped with ESD [electrostatic discharge] while transmitting data, the part injects all the energy back into the substrate and latches up. The easy way to solve this was to change the starting material to a richly doped P-type wafer, then deposit the lightly doped P-type epi substrate. It's a very well-known process.

"I go to this meeting where I'm proposing this epi process. Swanson looks at me and says, 'Reay, I can hire anybody off the street to come and put this on epi. In fact, if that's all it takes, I don't need a high-priced Stanford guy like you. I hear Maxim's hiring; maybe you oughta go over there!'

"After that meeting, I couldn't sleep for about three days. Eventually, I figured out how to solve it. What I didn't realize until later is that while most products were on the bipolar process, most new designs were on CMOS. So in production,

### **EE**Times D

the CMOS-to-bipolar ratio was about to change. Epi costs an extra \$30 per wafer. Our CMOS wafer costs, as a company, would have gone up 30%. By having a public beating of me, in front of the whole design group, Swanson made sure that we didn't start using epi for another two to three years, and the company made a lot of money, which we handed back as profit sharing. That was Bob's genius."

Gifford shared the same ability as Swanson. From Doluca's book, "Maximum Impact":

As always, whether negotiating for an event, a product price, or a company purchase, Gifford always walked into the deal with a strategy in mind. "He's trying to get the best out of everybody," says [Steve] Combs. "He's going to take whatever they said was their best and he's going to tell them it's crap ... knowing that they were going to do better when the real deal came through." No matter the situation, "he had his game face and he used it. He knew how to push people."

Said Reay, "I never worked for Gifford, but he was the same way. They're both good at reading people. They're really tough. Stories of throwing chairs against the wall, Swanson putting a pen through his fist — they're all true."

Doluca's account mirrors Reay's recollections. "Yes, Jack was a tough manager who perfected the art of tough love," Doluca writes. "Many are the unique and legendary water cooler stories shared

about him at tech companies in recent decades, and most are completely true."

#### LOOKING FORWARD

The analog thread of Silicon Valley history added another stitch in August of 2021, when Analog Devices completed the acquisition of Maxim, bringing together the three legendary high-performance analog companies (ADI acquired Linear in March 2017). ADI's legendary leader, Ray Stata, retired as chair of the board at ADI early in 2022, a role he served since 1973. He still frequently visits the company. The imprints of Swanson and Gifford, who passed away in 2008, remain in the people who carry forward the torch of analog semiconductors and other industries to which they have migrated.

Silicon Valley, always pushing forward, remains the center of the technology universe. Filling the vacuum of the Fairchild of the '60s are now Facebook, Google, Apple (the old guy of the group), and multitudes of software and internet companies, as well as those pushing the edge of technology in health care, artificial intelligence, and green energy, among other industries.

With analog semiconductors firmly embedded in the history of Silicon Valley, challenges and opportunities continue to emerge. The climate crisis, brought on by human-induced greenhouse gas emissions, now threatens human habitats across the globe. Silicon Valley suffers from drought and wildfires that plague California and many parts of the world. This crisis, however, means a challenge and an opportunity for passionate people to try and fail, to dig deep, to be entrepreneurial, and to solve problems. How can analog semiconductors help?

Reay turned again to history to answer that question: "Bob Dobkin did the first three-pin LDO linear regulator. He did it as a skunkworks project — really innovative. Now, LDOs are everywhere, just a standard thing. When I started, we did some of the first switching regulators, [and] TI was also doing them — it was an arms race. A lot of the innovation was driven by the digital side. The first digital processors were powered by linear regulators, but as the power levels kept going up, it just became obvious that was not a good approach, and you had to get more clever with the power architectures.

"There's been a nice steady progression of new types of architectures. The basic premise of converting one voltage to another as efficiently as possible, without heat and energy dissipation, and trying to shrink the size down as much as possible — that hasn't changed.

"There are lots of new and interesting architectures. The Silent Switcher is an interesting breakthrough because buck regulators have been around for a long time. Then all of a sudden, through some very clever observations, you can use magnetic fields to cancel each other out, and get the electromagnetic interference way down. Or you have the coupled inductor technology that came from Volterra and through Maxim, another example of really clever architecture. "What I've seen as the biggest change in the last 10 years is that the innovation in power design used to be silicon-based, and the packaging didn't change much," Reay said. "There were new architectures, processes, and materials – you bring in gallium arsenide and gallium nitride, for example. But about 10, maybe 15 years ago, the silicon wasn't changing as rapidly as the packaging was. All of a sudden, we started hiring a lot more packaging engineers. A lot of the innovation in trying to get the density in power was not coming from the silicon innovations; it was just as important to have innovations in how you did the package, such as going to copper pillars to get rid of the bond wires or using laminate substrates where you could put the bypass caps right on the die or using bus bars."

Reay noted, "You look at the density of what's going on in the µModules, where you're putting in discrete components, bare dies, bus bars, and it's all incorporated into a tiny space. The mechanical part of the design is just as important as the electrical part. I see the same thing with increasing voltages and the requirements of electric vehicles. There's been a lot of innovation in the high-voltage, high-power device types."

Where is all of this going? "More and more, you need to expand beyond the basic building blocks," Reay said. "But we can't forget that we have all of this analog expertise. We still have to invest in the basic analog functionality. The thing we [ADI] have going for us is this 50-year history of innovative analog design."

How about solving the climate crisis? "I think there are a lot of young people coming

### EE Times Do

out of school — including my son, who works at a green energy startup — who view the energy space as something we need to solve at a global level," said Reay. "I see a lot of young people who really think about this; they're thinking, 'Is the product I'm working on going to have an advantage in the long run?' I didn't think about that at all.

"There are a lot of interesting developments that we don't even hear about — a lot of people, startups, and excitement," he said. "The solution to these problems involves looking at human behavior: Where is all of the energy going? Some of this is not rocket science.

"I talk to young people; I look at them and I'm so excited for them," he added. "They're on the ground floor of a bunch of new stuff. I hope they can all feel the same excitement that I felt at that age. It makes me feel confident about the future."

The untold future of Silicon Valley will undoubtedly rely on characters — those who stick to their passions, are willing to fail, and dig deep to solve difficult problems. As the analog industry and technology at large follow an unpredictable, unique path, the future of climate solutions and energy efficiency will also be unique and unpredictable. The hope, excitement, opportunities, and challenges will always be there. So here's to another 50 years of passion, failure, digging deep, and solving problems.

Reay concluded with some sound advice: "Whatever it is that got you into the business in the first place, that you really love, and you're really good at, keep doing that."

The Next Silicon Frontier 35

### A 50-YEAR HISTORY OF THE MICROCONTROLLER

#### BY TIM BURGESS AND BERND WESTHOFF

EE Times 59

Microcontrollers (MCUs) have been with us since the early 1970s and are now celebrating 50 years of existence. During that half-century, MCUs have become essential components in the electronics toolbox. Starting from humble beginnings as programmable calculator chips, MCUs are now integral to the design of electronic products including automobiles, medical products, consumer devices, toys, televisions, radios, appliances, and many other embedded applications occupying every electronics niche. MCUs punch far above their weight class. That's why they've become ubiquitous.

Intel introduced the first commercial, single-chip microprocessor, the 4004, on Nov. 15, 1971. Although it was designed for embedded applications (what we now call "edge" applications), the 4004 microprocessor required many additional chips to create a complete system. The 4004 lacked on-chip RAM, ROM, and I/O functions required by an MCU.